SLUAAM4 December 2023 BQ76905 , BQ76907

4 I2C With CRC

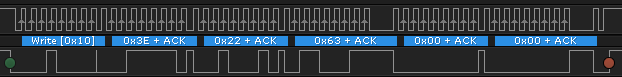

The I2C interface on the BQ7690x family includes an optional CRC check. The CRC feature can be enabled in the Settings:Configuration:I2C_Config[CRC] register. If this register is changed while using BQStudio, then BQStudio can be restarted so that it can detect the new communication mode. Two examples follow of I2C waveform captures with the CRC check enabled.

The CRC for the first data byte is computed on all of the bytes after the I2C start up to and including the first data byte. For every data byte after the first byte, the CRC byte is computed for only that byte. In Figure 4-1, using the FET_ENABLE subcommand, the CRC for the first byte is computed for [0x10 0x3E 0x22] - the resulting CRC is 0x63. The CRC for the second byte [0x00] is 0x00.

Figure 4-1 Captured I2C Waveform for

FET_ENABLE Subcommand With CRC

Figure 4-1 Captured I2C Waveform for

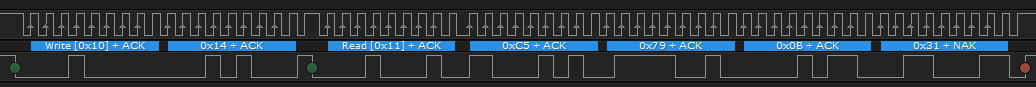

FET_ENABLE Subcommand With CRCThe VCell 1 command is used in Figure 4-2, and the CRC for the first byte is computed for [0x10 0x14 0x11 0xC5]. The resulting CRC is 0x79. The CRC for the second byte [0x0B] is 0x31.

Figure 4-2 Captured I2C Waveform for

VCell 1 Command With CRC

Figure 4-2 Captured I2C Waveform for

VCell 1 Command With CRC