SLUAAP7 January 2024 BQ76905 , BQ76907

2.2 External Cell-Balancing Circuit Design Using N-Channel FETs

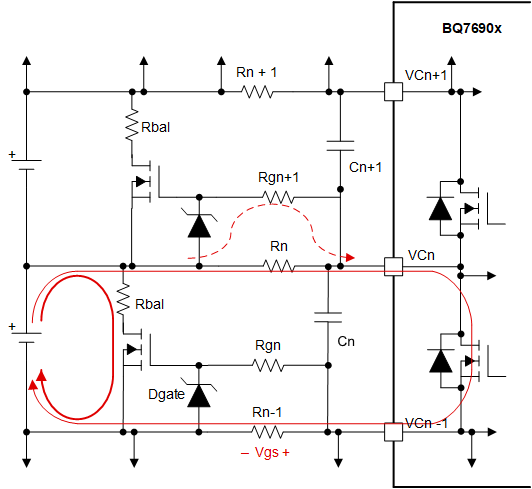

For applications that need higher cell balancing current, external FETs are often used. When using external FETs, the cell input resistors can be increased to the maximum recommended value of 1kΩ. Increasing the resistor size will help to provide enough voltage across the gate of the FET. In Figure 2-3, as the internal FET is turned on inside the device, the current flowing through Rn-1 provides the VGS for the external FET.

Figure 2-3 Balancing Circuit Using

External N-channel FETs

Figure 2-3 Balancing Circuit Using

External N-channel FETsCare must be taken to select an external FET with a low RDSON defined at low VGS. For example, say the minimum cell balance voltage is 3.9V. The external FET can have an RDSON defined at or below 3.9V x 100 / (100 + 100 + 80) = 1.39V.

A Zener diode is needed to protect the external FET gate from pack transients. For example, in the event of a short across the pack in a 7-cell battery, Cell 7 would have approximately 28V across Rn during the event and the opposite transient at the release of the short circuit. The gate voltage can be connected through a resistor to limit the current when the diode conducts. (During normal operation the Zener will not conduct).

For Figure 2-3, the circuit was designed with an Rn of 100Ω and Rgn of 1kΩ. The Rbal resistor is set to 50Ω for a balance current of approximately 77mA through the external FET at 4V. At this cell voltage, an additional approximately 15mA of current flows through the internal FET of the device for a total balancing current of close to 92mA. An N-channel MOSFET was selected with an RDSON defined for low VGS down to 1.4V.

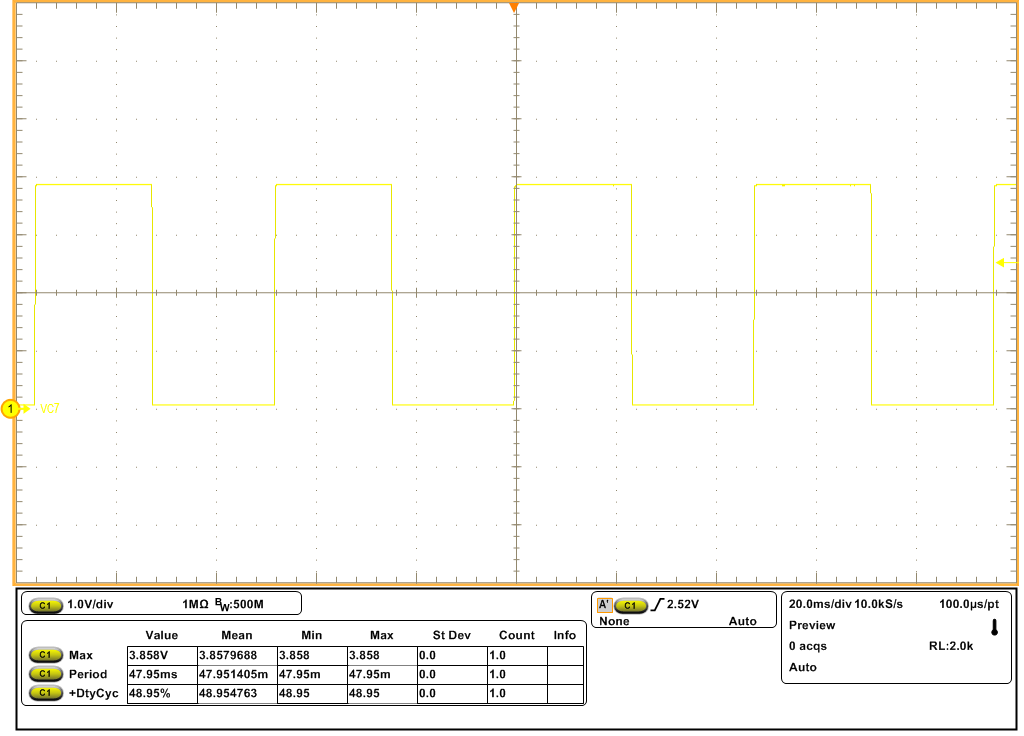

Figure 2-4 BQ76907 Cell Balancing With

N-Channel FETs, Cell 7 (VC7) Rbal_voltage Approximately = 3.86V

Figure 2-4 BQ76907 Cell Balancing With

N-Channel FETs, Cell 7 (VC7) Rbal_voltage Approximately = 3.86V