-

Parallel Operation of TPS2663 eFuses

Parallel Operation of TPS2663 eFuses

Trademarks

All trademarks are the property of their respective owners.

1 Introduction

The TPS2663 device incorporates protection features such as inrush current management, adjustable overcurrent limit, short-circuit protection, overvoltage and input reverse polarity protection. Figure 1-1 shows an application schematic of the TPS26631 feeding a downstream DC-DC converter in a PLC system. The capacitor CdVdT on the dVdT pin sets the output voltage slew-rate and hence the inrush current level where as the resistor RILIM sets the current limit (ILIM) which the device needs to limit to under fault conditions. The device offers a B-FET driver to control an external N-channel FET ‘Q1’ for reverse current and reverse polarity protection which simplifies designs requiring class-A performance during system tests like IEC61000-4-5 surge tests as well as input supply brown-out tests.

The maximum current the TPS2663 can support is up to 6 A. However the device can be used in parallel configuration with multiple TPS2663 devices to achieve higher output currents which is often required in many industrial systems. This report presents how the TPS2663 can be used in parallel operation to achieve higher output currents as well as to demonstrate the performance benefits it brings to the system with its integrated protection functions.

2 Parallel Configuration

The basic principle of eFuse parallel operation and the design considerations are covered in the Achieve 20-A Circuit Protection and Space Efficiency Using Paralleled eFuses Application Report(1). The same concept is applicable for TPS26631 parallel operation. The key points from the Achieve 20-A Circuit Protection and Space Efficiency Using Paralleled eFuses Application Report(1) are summarized in the rest of this section in the context of TPS26631.

- During start-up, equal current

sharing among the parallel-connected eFuses is needed to ensure successful

start-up. To achieve that,

- The UVLO, OVP, SHDNb pins of all the parallel-connected eFuses are connected together for synchronizing the ON or OFF operation

- The dVdT pins of all the eFuses are connected together to ensure uniform output ramp rate and equal dynamic power stress

- During steady-state operation, the current sharing is decided by the RDS(on) mismatch. The device having the lower RDS(on) shares more current than the rest of the devices. However, the self-heating effect due to positive temperature characteristics of the MOSFET helps to a larger extent towards equal load current distribution in parallel configuration.

- During overload operation, the inherent current source characteristic of eFuse forces all the parallel-connected eFuses to operate in current-limiting mode. For the TPS26631, each device should have its own current-limiting resistor (RILIM) as demanded by the internal current loop architecture.

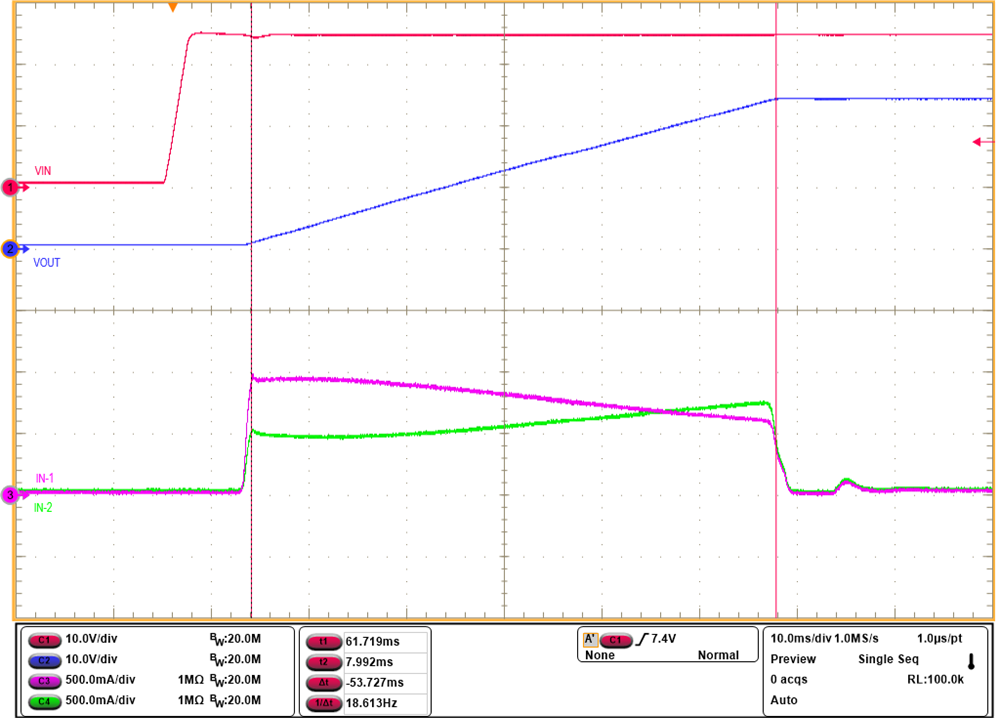

Figure 2-2 Current Sharing Between the Devices During Start-up in dVdT mode

Figure 2-2 Current Sharing Between the Devices During Start-up in dVdT modeFigure 2-1 illustrates the circuit configuration of two TPS26631 devices in parallel. A single blocking FET Q1 on the primary eFuse is enough for reverse current blocking. Figure 2-2 shows the current sharing during start-up with dVdT pins together. Even though the ramp rate of the dVdT pin is the same for both the devices, the mismatch in the internal dVdT gain and the internal FET characteristics leads to unequal current sharing during start-up. For uniform current distribution while starting up into large loads, current limited start-up is recommended as follows

- Leave dVdT pins OPEN

- Use RILIM resistor switch network at the ILIM pin. The RILIM_Low sets the inrush current. After successful start-up, PGOOD asserts high which sets the overload current limit as per (RILIM_Low || RILIM_High) at the ILIM pin

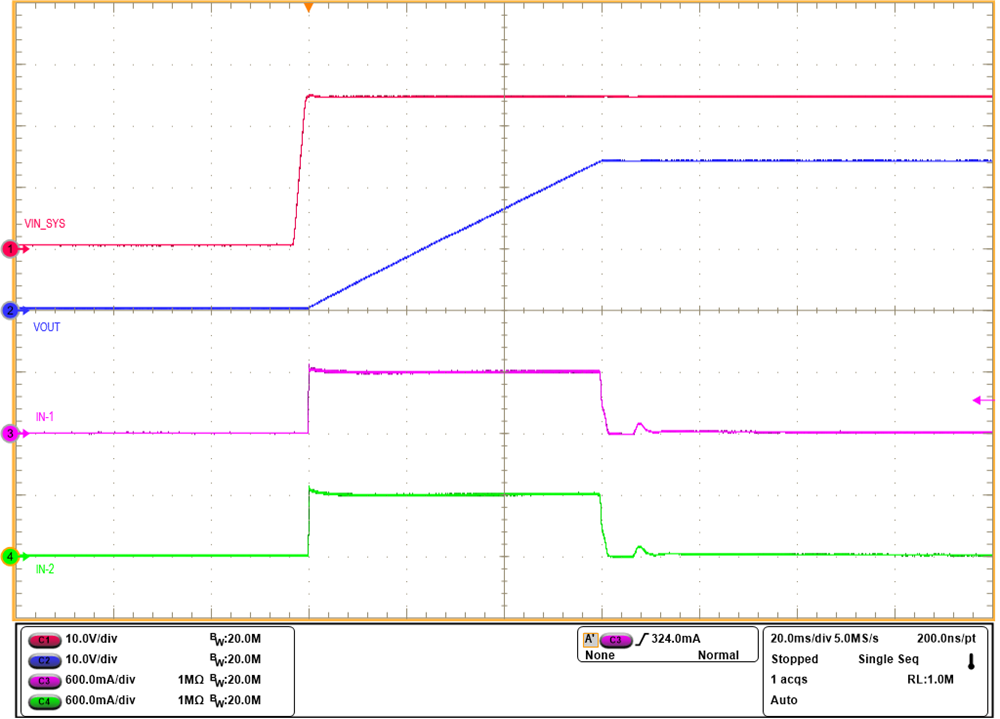

The modified parallel circuit configuration is illustrated in Figure 2-3 and the corresponding start-up waveform demonstrating equal start-up current between two TPS26631 devices is shown in Figure 2-4. In this application report, RILIM resistor switch network is considered in the design example as it ensures uniform current sharing under all the stressful events.

Figure 2-4 Current Sharing Between the Devices During Start-up in Current-Limit

Mode

Figure 2-4 Current Sharing Between the Devices During Start-up in Current-Limit

Mode3 Design Example

An example of designing four TPS26631 eFuse parallel circuits is considered in this section.