SLVUD04 August 2024 TPSM83102

- 1

- Description

- Features

- 4

- 1Evaluation Module Overview

- 2Hardware

- 3Software

- 4Hardware Design Files

- 5Additional Information

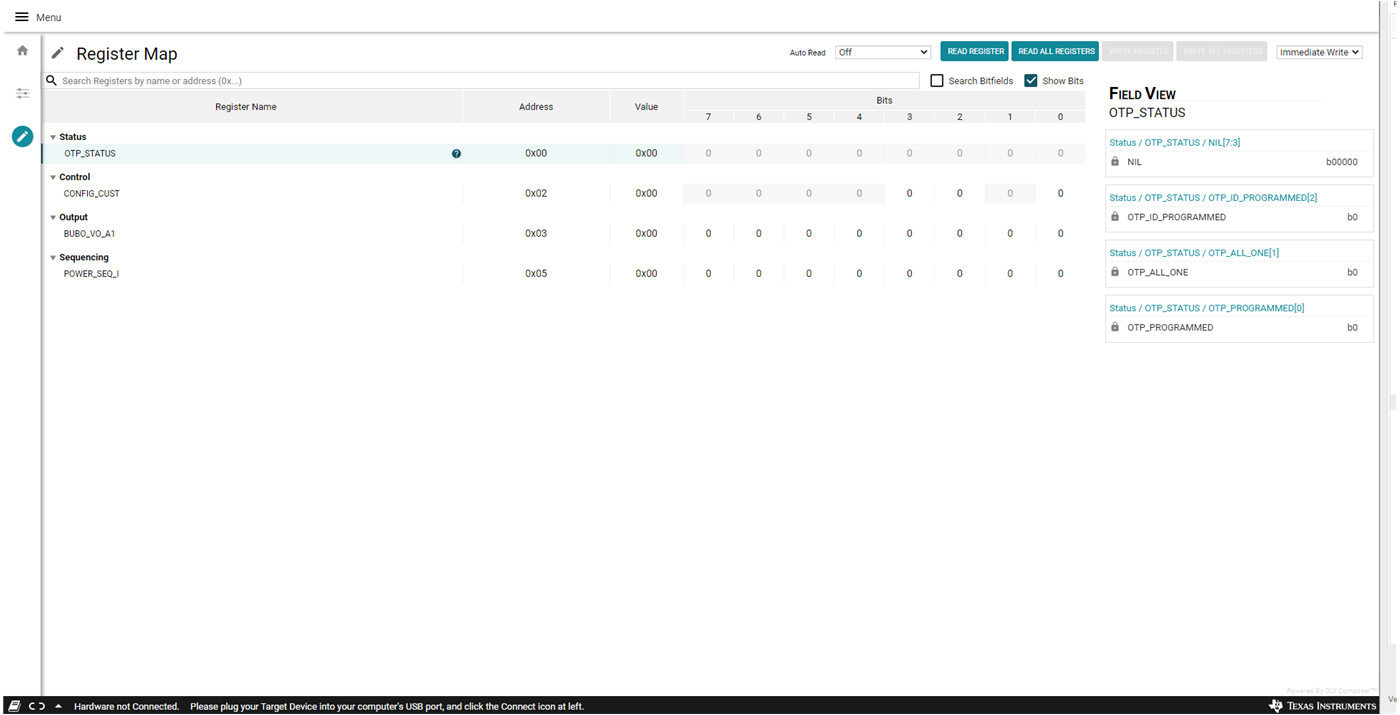

3.3.3 Register Map Screen

The Register Map screen shows a register-wise view of all parameters. Here, single registers can be read or written to the device (if applicable). Refer to Section 3.4 for a detailed description of the TPSM83102 and TPSM83103 registers.

Figure 3-4 GUI Register Map Screen

Figure 3-4 GUI Register Map Screen