SLYT850 February 2024 UCD3138

4 RHPZ effect and solution

The loop compensation for charge-mode control is simple when the PFC operates in DCM. Loop compensation becomes a challenge, however, because a right-half-plane zero (RHPZ) appears in the control loop when the boost converter operates in CCM [3]. The RHPZ induces a phase drop that negatively impacts the potential phase margin of the control loop. Equation 7 expresses the small-signal model for the control loop as:

where RLOAD is the output load of PFC, D is the pulse-width-modulation duty cycle, and .

Equation 7 clearly shows the RHPZ ωZ. Its frequency varies with load, boost inductance and D (D varies with the input and output voltage), which makes loop compensation very difficult.

To eliminate the RHPZ, Equation 8 modifies the feedback signal:

Figure 7 modifies the control law, where you can see that IREF is now modulated by VIN, not by VIN2.

Figure 7 Charge-mode control law for

PFC after eliminating RHPZ.

Figure 7 Charge-mode control law for

PFC after eliminating RHPZ.With this modification, Equation 9 expresses the small-signal model of the control loop as:

The RHPZ disappears and the system becomes a first-order system, which is very easy to compensate.

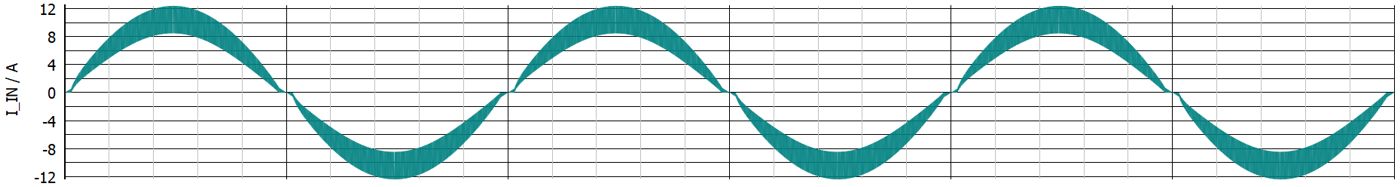

Figure 8 illustrates the verification of the new control algorithm through simulation, achieving a sinusoidal input current waveform.

Figure 8 Simulation result: a

sinusoidal input current waveform.

Figure 8 Simulation result: a

sinusoidal input current waveform.