SNVS256E November 2003 – October 2024 LP3943

PRODUCTION DATA

- 1

- 1Features

- 2Applications

- 3Description

- 4Pin Configuration and Functions

- 5Specifications

- 6Detailed Description

- Application and Implementation

- 7Device and Documentation Support

- 8Revision History

- Mechanical, Packaging, and Orderable Information

6.5.3 Transferring Data

Every byte put on the SDA line must be eight bits long with the most significant bit (MSB) being transferred first. The number of bytes that can be transmitted per transfer is unrestricted. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the 9th clock pulse, signifying an acknowledge. A receiver which has been addressed must generate an acknowledge after each byte has been received.

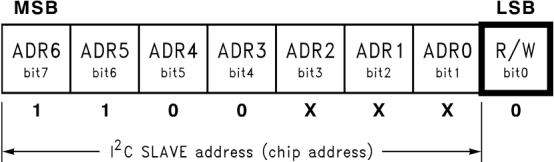

After the START condition, a chip address is sent by the I2C master. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LP3943 hardwires bits 7 to 4 and leaves bits 3 to 1 selectable, as shown in Figure 6-3. For the eighth bit, a 0 indicates a WRITE and a 1 indicates a READ. The LP3943 supports only a WRITE during chip addressing. The second byte selects the register to which the data is written. The third byte contains data to write to the selected register.

Figure 6-3 Chip Address Byte

Figure 6-3 Chip Address Byte

However, if a READ function is to be accomplished, a WRITE function must precede the READ function, as shown in Figure 6-5.