SNVU751 October 2020 LP875761-Q1

6 Board Layout

This section describes the board layout of the LP875761Q1EVM. See the LP875761-Q1 data sheet for specific PCB layout recommendations.

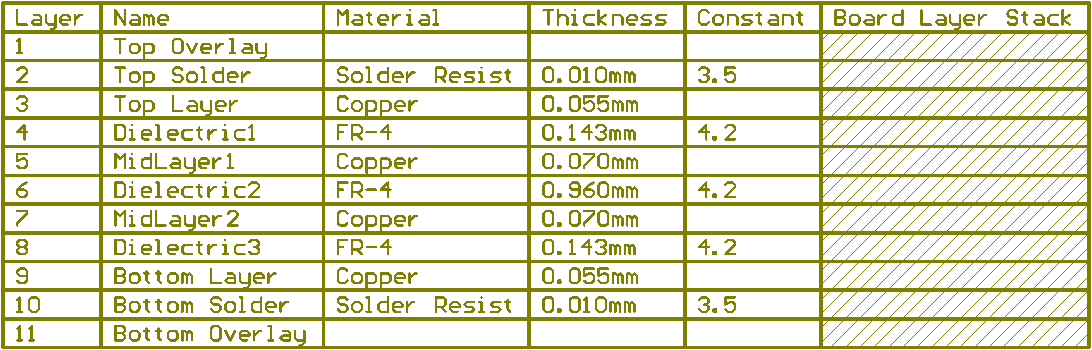

The board is constructed on a 4-layer PCB. using 55-µm copper on top and bottom layers to reduce resistance and improve heat transfer.

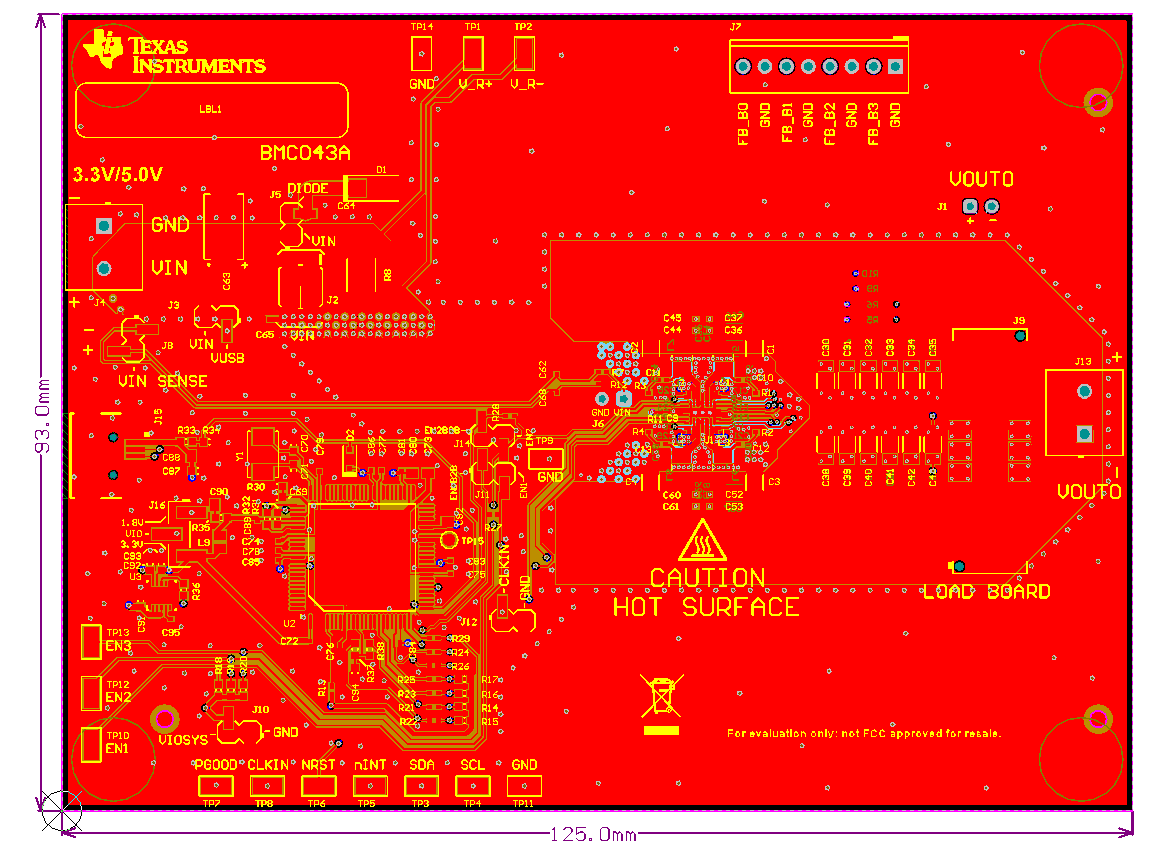

Board stack-up is shown in Figure 6-1. Figure 6-2 shows the top view of the entire board and Figure 6-3 through Figure 6-8 show the component placement, layout, and 3D view close to the LP875761-Q1 device.

Figure 6-1 Board Stack-Up

Figure 6-1 Board Stack-UpThe design utilizes dual side placement of the components. This allows placement of the inductors next to the LP875761-Q1 device for reducing SW node area for improved efficiency and reduced EMI. SW nets have also snubber components to reduce SW pin spiking and EMI. The input capacitors can be placed very close to the LP875761-Q1 device, to bottom side, to keep parasitic inductances low, and there is also space for input filters for further EMI reduction.

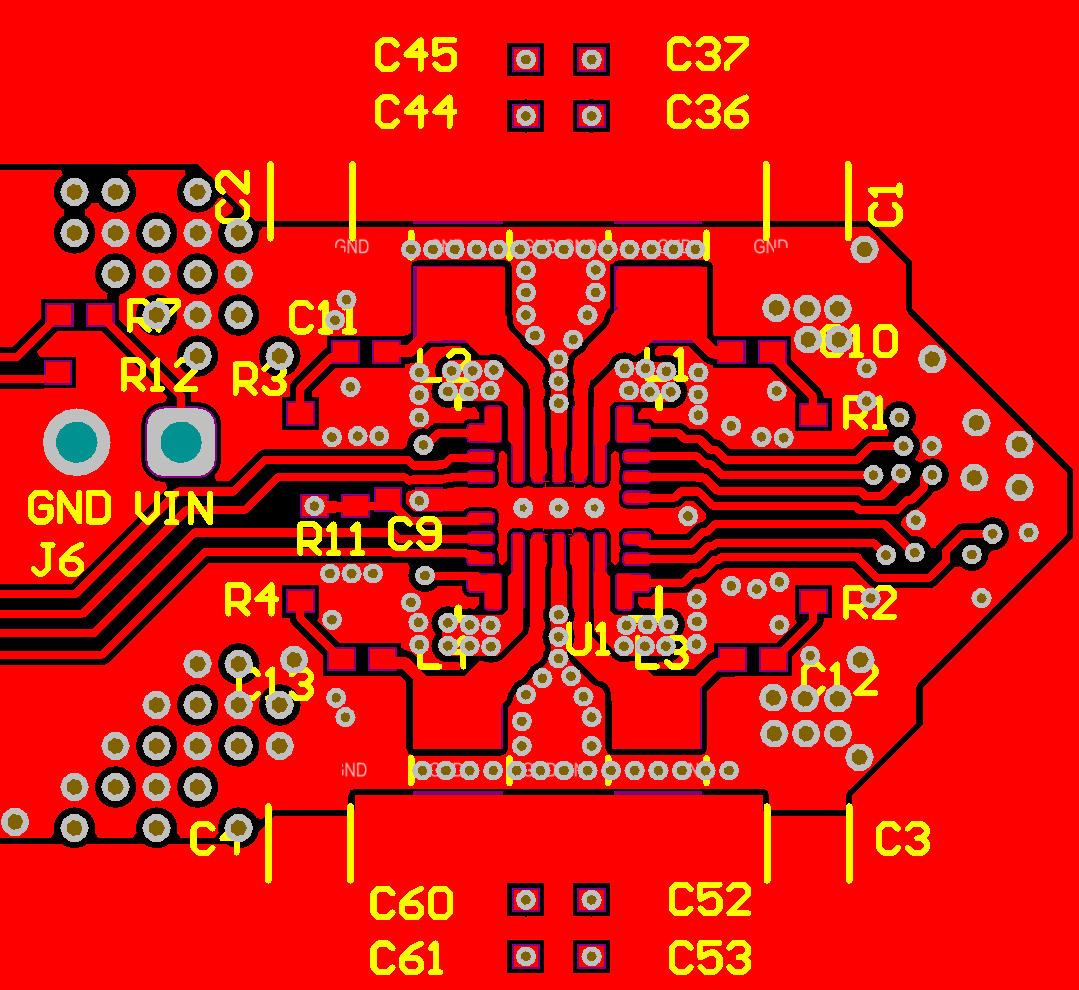

Figure 6-2 Top View of the

LP875761-Q1EVM

Figure 6-2 Top View of the

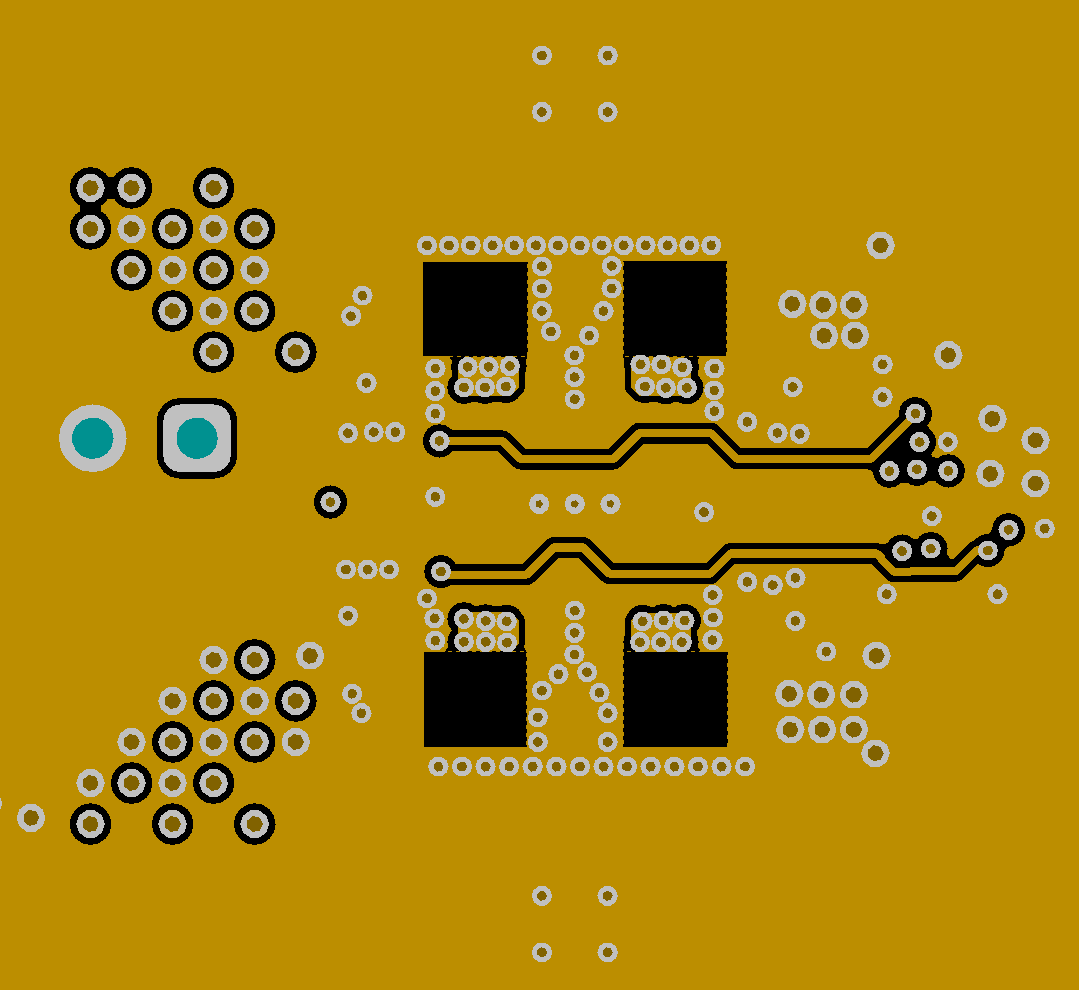

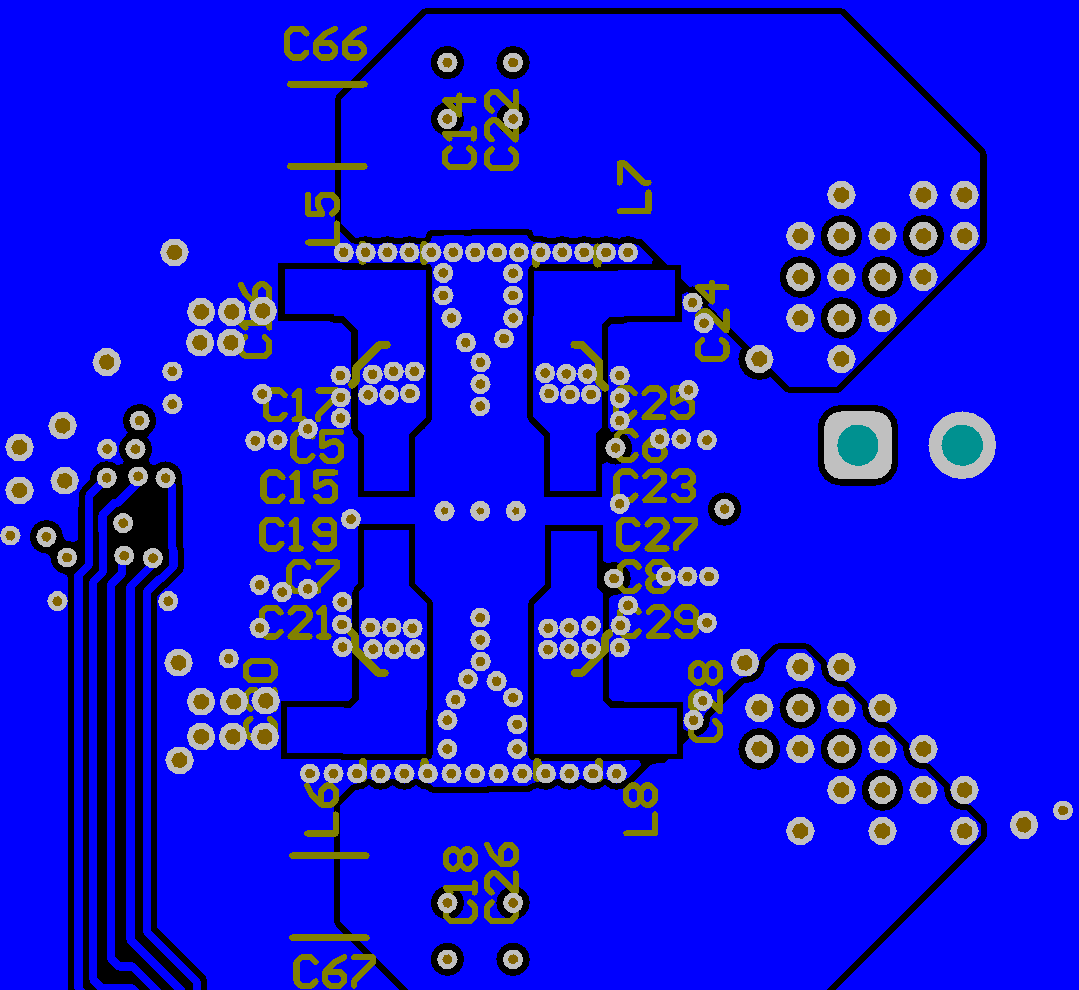

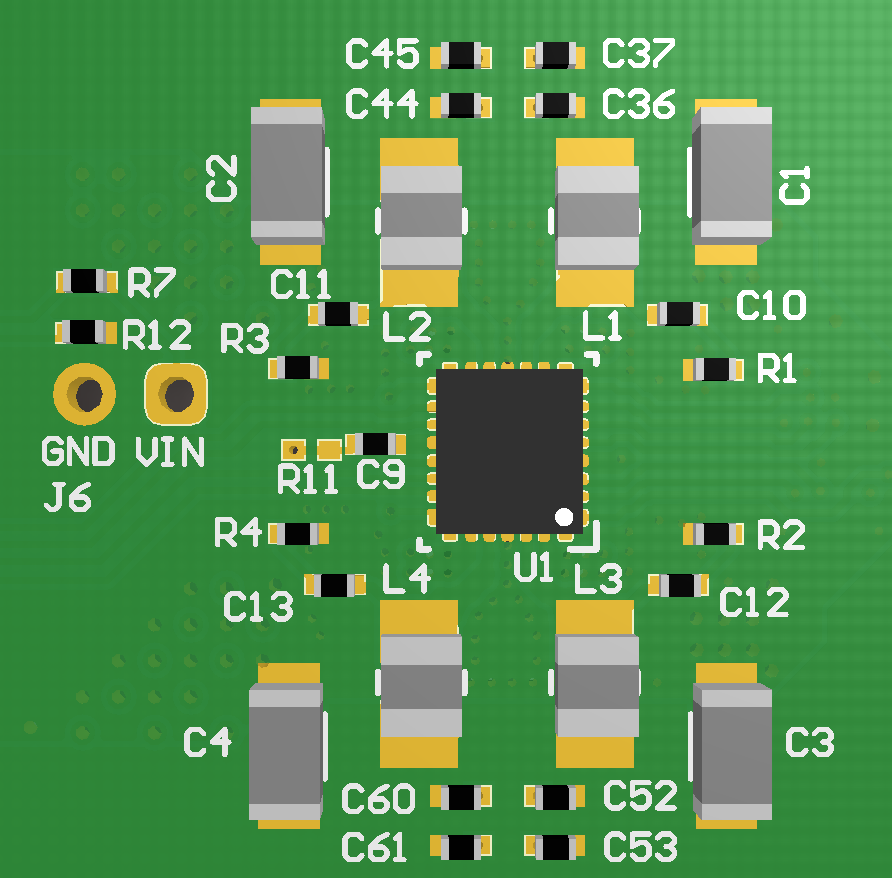

LP875761-Q1EVM Figure 6-3 Component Placement Top

Layer

Figure 6-3 Component Placement Top

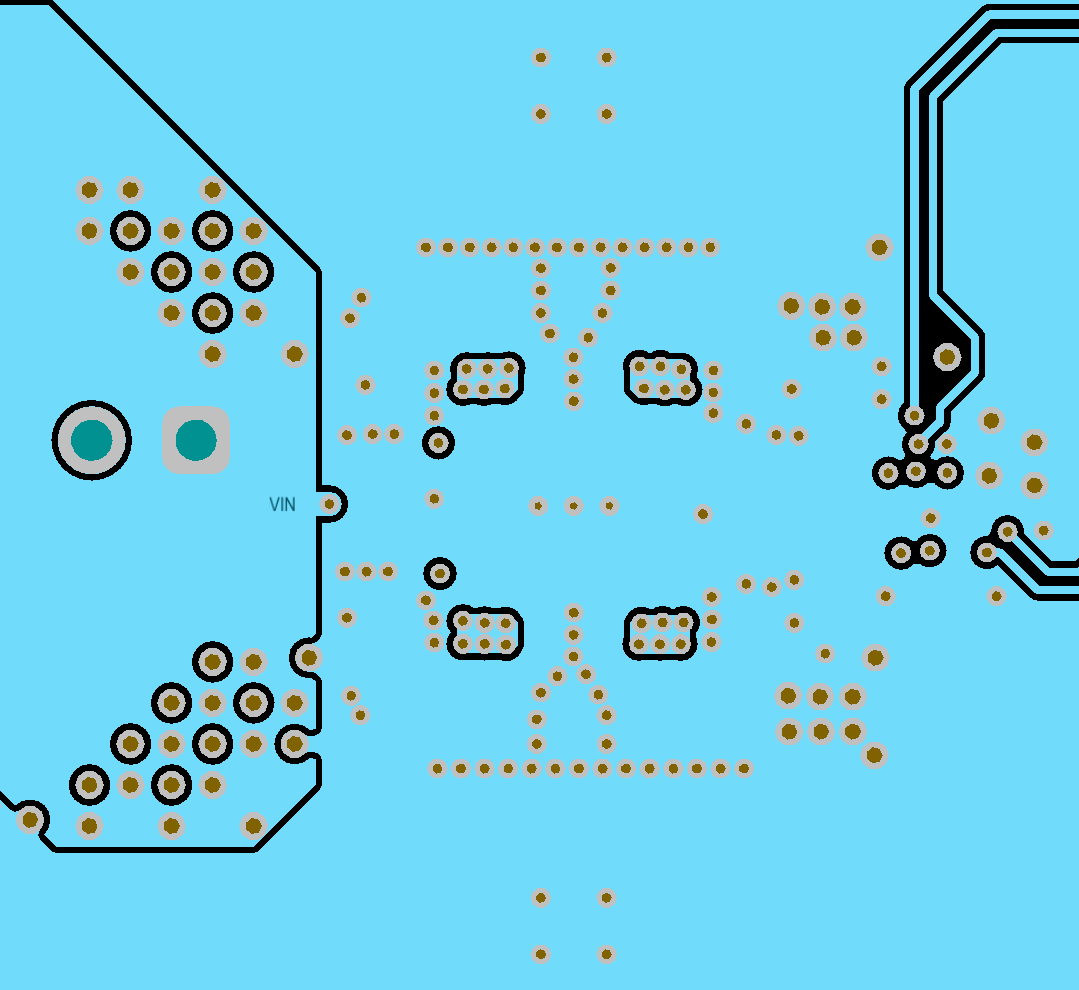

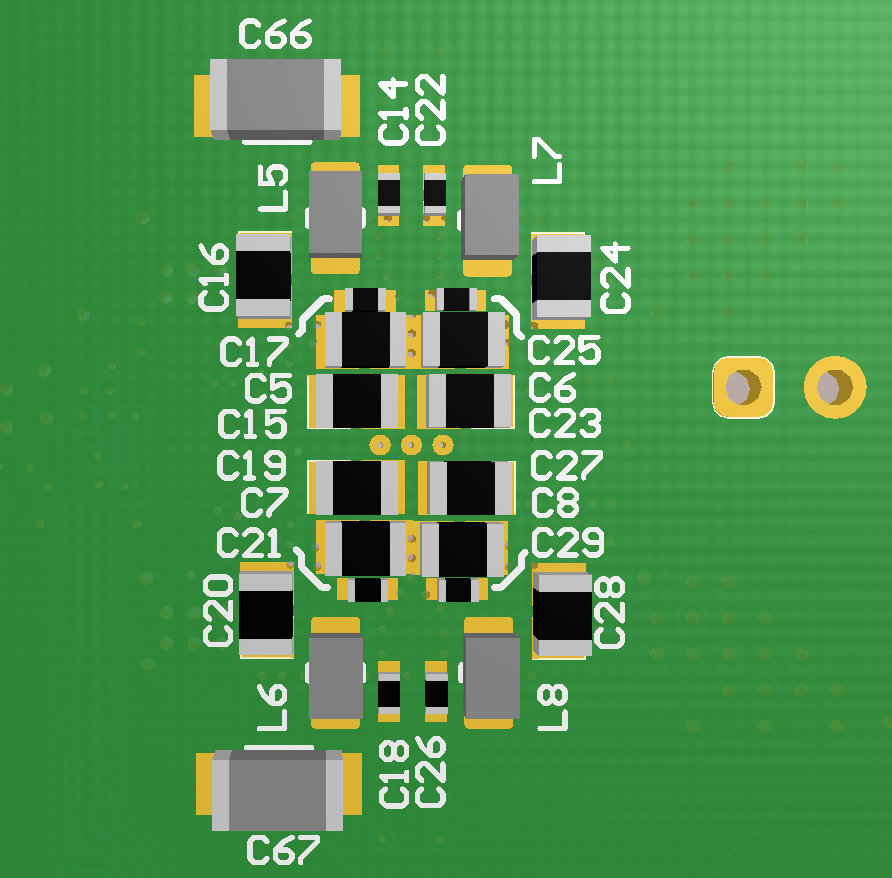

Layer Figure 6-4 Component Placement Bottom

Layer

Figure 6-4 Component Placement Bottom

Layer