SPRABJ8B September 2022 – November 2023 AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P4 , AM263P4-Q1

5.1 SOP Signal Implementation

Each SOP bootmode selection signal is multiplexed with a subset of OSPI/QSPI and SPI peripheral functional mode signals. For all signal descriptions, see the Signal Description tables in the AM263x Sitara™ Microcontroller Data Sheet and AM263Px Sitara™ Microcontroller Data Sheet. The SOP signal descriptions are excerpted in Figure 5-1.

| AM263x/AM263Px Pin Number | Primary Pinmux Signal | SOP Mode Signal |

|---|---|---|

| N1 | OSPI0/QSPI0_D0 | SOP[0] |

| N4 | OSPI0/QSPI_D1 | SOP[1] |

| A11 | SPI0_CLK | SOP[2] |

| C10 | SPI0_D0 | SOP[3] |

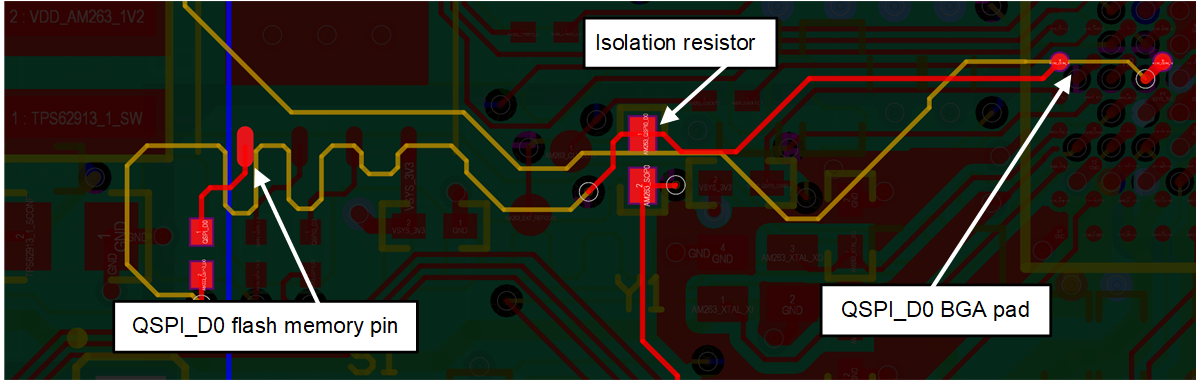

Because of this SOP/functional-mode multiplexing additional care must be taken in schematic and layout to ensure that the SOP mode selection resistors, jumpers or switch paths are routed in such a way that the SOP mode branches do not present inductive stubs to the functional mode signal paths. Failing to take care of this may result in non-functional OSPI/QSPI or SPI interfaces.

![Excerpt From AM263x Launchpad Schematic – SOP[3:0] Functional and SOP Paths GUID-20220808-SS0I-M9WB-WBWX-WCXKGR5WNDSQ-low.svg](/ods/images/SPRABJ8B/GUID-20220808-SS0I-M9WB-WBWX-WCXKGR5WNDSQ-low.svg) Figure 5-1 Excerpt From AM263x Launchpad Schematic – SOP[3:0] Functional and SOP Paths

Figure 5-1 Excerpt From AM263x Launchpad Schematic – SOP[3:0] Functional and SOP PathsIn the AM263x and AM263Px Control Card and Launchpad designs this SOP mode isolation is accomplished by including a 10KΩ resistor in the SOP signal path. The resistor is placed such as one pad is as close to the AM263x BGA pad and in-line with the functional mode path. This creates a layout where the additional stub length necessary to breakout the SOP path will only minimally impact the functional mode operation of the signals, as shown in Figure 5-2 and Figure 5-3.

![Excerpt From AM263x Launchpad Layout – All SOP[3:0] Functional and SOP Paths GUID-20220808-SS0I-TPHJ-4TPV-TMLN1N96KL5J-low.png](/ods/images/SPRABJ8B/GUID-20220808-SS0I-TPHJ-4TPV-TMLN1N96KL5J-low.png) Figure 5-2 Excerpt From AM263x Launchpad Layout – All SOP[3:0] Functional and SOP Paths

Figure 5-2 Excerpt From AM263x Launchpad Layout – All SOP[3:0] Functional and SOP Paths  Figure 5-3 Excerpt From AM263x Launchpad Layout – Highlighting SOP0/QSPI_D0 Path and SOP Isolation Resistor

Figure 5-3 Excerpt From AM263x Launchpad Layout – Highlighting SOP0/QSPI_D0 Path and SOP Isolation Resistor