SPRACN9F May 2023 – August 2024 AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA821U , DRA821U-Q1 , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1 , TDA4AEN-Q1 , TDA4AH-Q1 , TDA4AL-Q1 , TDA4AP-Q1 , TDA4APE-Q1 , TDA4VE-Q1 , TDA4VEN-Q1 , TDA4VH-Q1 , TDA4VL-Q1 , TDA4VM , TDA4VM-Q1 , TDA4VP-Q1 , TDA4VPE-Q1

- 1

- Jacinto7 AM6x/TDA4x/DRA8x LPDDR4 Design Guidelines

- Trademarks

- 1Overview

-

2LPDDR4 Board Design and Layout Guidance

- 2.1 LPDDR4 Introduction

- 2.2 LPDDR4 Device Implementations Supported

- 2.3 LPDDR4 Interface Schematics

- 2.4 Compatible JEDEC LPDDR4 Devices

- 2.5 Placement

- 2.6 LPDDR4 Keepout Region

- 2.7 Net Classes

- 2.8 LPDDR4 Signal Termination

- 2.9 LPDDR4 VREF Routing

- 2.10 LPDDR4 VTT

- 2.11 CK, CMD_ADDR, and CTRL Topologies

- 2.12 Data Group Topologies

- 2.13 CK, CMD_ADDR, and CTRL Routing Specification

- 2.14 Data Group Routing Specification

- 2.15 Channel, Byte, and Bit Swapping

- 3LPDDR4 Board Design Simulations

- 4Revision History

3.6.4 Simulation Results

The simulation results are provided for the LPDDR4 interface from a 10 layer design. These simulation targets must be met to ensure the design will operate at the desired level of performance.

CA simulations need to be verified at the DRAM pin/BGA. This includes:

- Minimum ring-back margins at high/low levels (JEDEC)

- Vix_CK ratio (JEDEC)

- Jitter/noise margins with respect to the eye mask (JEDEC)

- Peak-peak power noise

Figure 3-11 LPDDR4 Simulation Results for

CA

Figure 3-11 LPDDR4 Simulation Results for

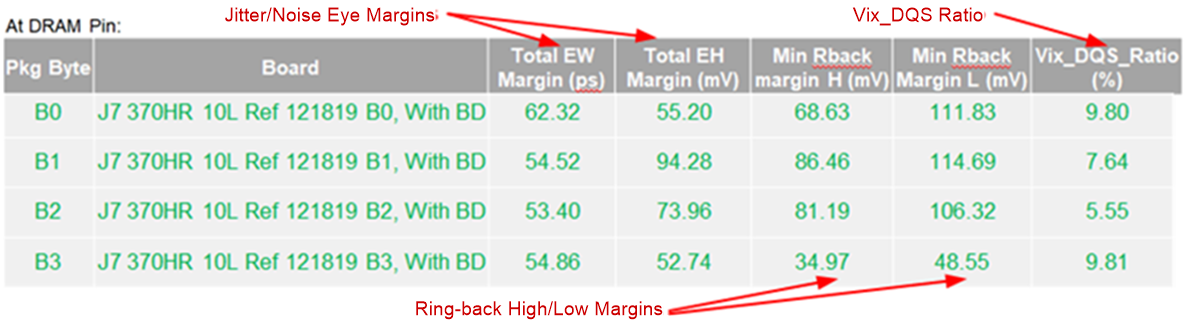

CAData write simulations need to be verified at both the DRAM BGA pin and the DRAM pad. This includes:

- Minimum ring-back margins at high/low levels (JEDEC)

- Vix_CK ration (JEDEC)

- Jitter/noise margins with respect to the eye mask (JEDEC)

- Peak-peak power noise

Figure 3-12 LPDDR4 Simulation Results for

Write

Figure 3-12 LPDDR4 Simulation Results for

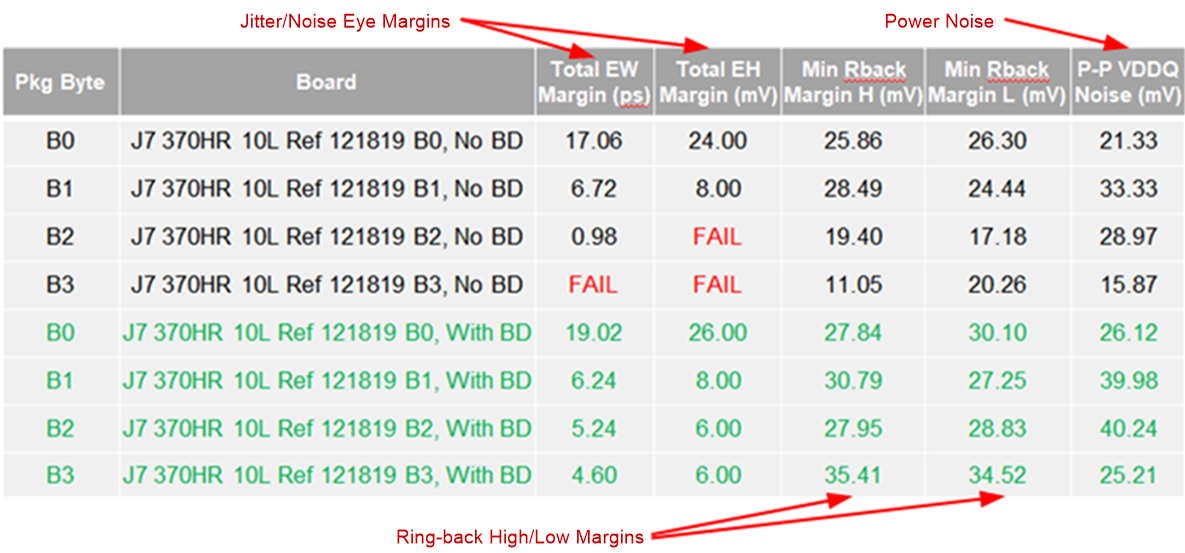

WriteData read simulations need to be verified at SOC. This includes:

- Minimum ring-back margins at high/low levels

- Jitter/noise margins with respect to the eye mask

- Peak-peak power noise

Figure 3-13 LPDDR4 Simulation Results for

Read

Figure 3-13 LPDDR4 Simulation Results for

ReadThe simulations results for read includes two sets for data, black and green. The black shows the design failed, as several bytes failed to meet the eye margins. The green is the simulation results of the same design, but with back-drilling the via stubs applied.