SPRACY3 June 2021 F29H850TU , F29H859TU-Q1 , TMS320F280023C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040C-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280048C-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28076 , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.2.2 Output Selection

Two extra GPIO pins are needed to export the CLB output signals, with OUTPUT X-BAR and CLB X-BAR. For example, configure GPIO16 and GPIO17 as OUTPUT X-BAR with the PINMUX settings.

GPIO_setPadConfig(16, GPIO_PIN_TYPE_STD);

GPIO_setPinConfig(GPIO_16_OUTPUTXBAR7);

GPIO_setDirectionMode(16, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(17, GPIO_PIN_TYPE_STD);

GPIO_setPinConfig(GPIO_17_OUTPUTXBAR8);

GPIO_setDirectionMode(17, GPIO_DIR_MODE_OUT);And then, configure OUTPUT-XBAR OUTPUT7 and OUTPUT8 as CLB OUT4 and OUT5, which are enabled for EPWM5B and EPWM6B, respectively.

// Configure OUTPUT-XBAR OUTPUT7 as CLB1_OUT4

XBAR_setOutputMuxConfig(XBAR_OUTPUT7, XBAR_OUT_MUX01_CLB1_OUT4);

XBAR_enableOutputMux(XBAR_OUTPUT7, XBAR_MUX01);

// Configure OUTPUT-XBAR OUTPUT8 as CLB1_OUT5

XBAR_setOutputMuxConfig(XBAR_OUTPUT8, XBAR_OUT_MUX03_CLB1_OUT5);

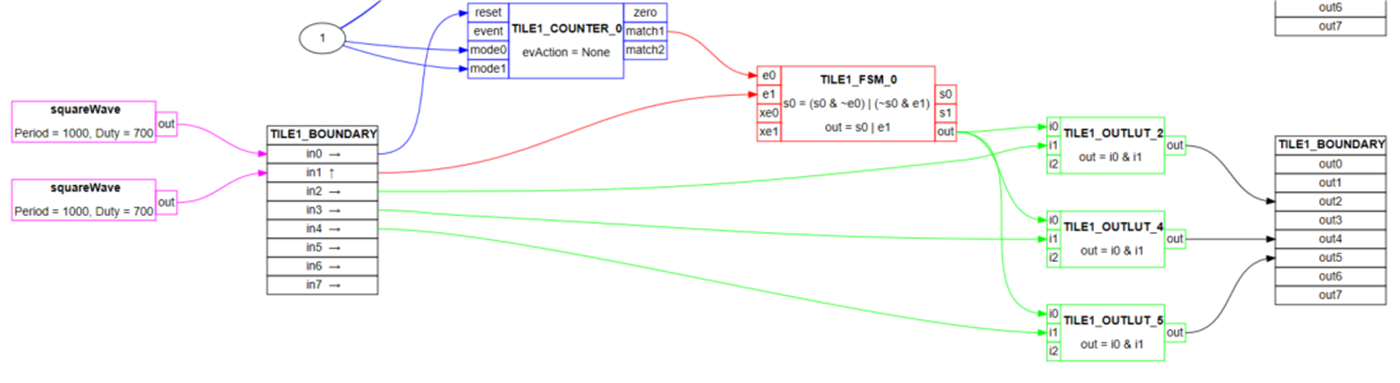

XBAR_enableOutputMux(XBAR_OUTPUT8, XBAR_MUX03);Since EPWM5B and EPWM6B share the same delayed protection logic with EPWM1 and EPWM2, Figure 5-1 shows the inner signal connectivity for CLB Tile 1.

Figure 5-1 CLB Tile 1 Inner Signal

Connectivity

Figure 5-1 CLB Tile 1 Inner Signal

Connectivity