SPRAD15 March 2022 F29H850TU , F29H859TU-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28375D , TMS320F28376D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28378D , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P550SJ , TMS320F28P559SJ-Q1 , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.1 Phase 3 PWM Consideration

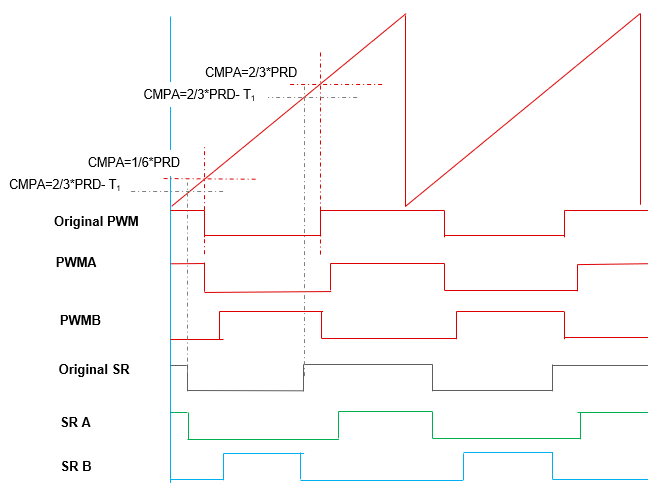

The PWM configuration of 3rd phase is shown in Figure 3-1. By following the principles mentioned above, the PWM can be generated easily. One special consideration is to make sure the comparator value for SR PWM always makes sense, which means:

CMPBS= CMPBP-t1 >0

CMPAS= CMPAP-t1 <PRD

Considering CMPBP =1/6*PRD and CMPAP =2/3*PRD:

T1<1/6*PRD

Normally, the T1 value is much smaller than PRD, and the conditions could be satisfied naturally. The condition needs to be checked especially when there is a huge frequency change or the PWM frequency is high. Note that if the loaded value of CMPx exceeds 0-PRD value range, the counter would never reach the comparator value and the configured action may not happen as expected. For information that shows the behavior if CMPA/CMPB is greater than the period, see the "Behavior if CMPA/CMPB is Greater than the Period" table within the technical reference manual.

Figure 3-1 Phase 3 PWM Generation Logic

Figure 3-1 Phase 3 PWM Generation Logic