SPRAD62 February 2023 F29H850TU , F29H859TU-Q1 , TMS320F280023C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038C-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

- Abstract

- Trademarks

- 1Introduction

- 2Serial Port Design Methodology

- 3Example A: Using the CLB to Input and Output a TDM Stream in Audio Applications

- 4Example B: Using the CLB to Implement a Custom Communication Bus for LED Driver in Lighting Applications

- 5References

3.7.4 Testing Data Integrity

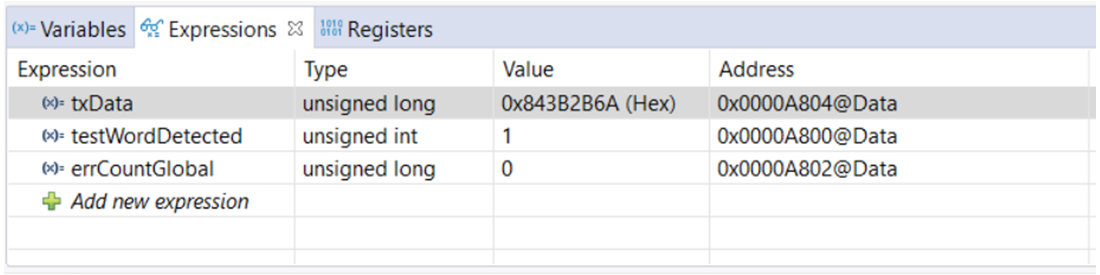

To test data integrity, the F28388D sends an incrementing data pattern to the F280025C. The F280025C checks the incoming data against expected data and generates a flag if any errors are detected. The F280025C echoes back all data received to the F28388D. Finally, the F28388D checks all incoming data for errors. Figure 3-17 shows a snap shot of the F28388D monitoring in progress. Note that no errors were detected by either the F280025C or the F28388D during the transmission of the entire 32-bit range.

Figure 3-17 F28388D Monitoring Incoming

TDM Traffic

Figure 3-17 F28388D Monitoring Incoming

TDM Traffic