TIDUF65 March 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Hardware, Software, Testing Requirements, and Test Results

- 5Performance Comparison with Competitor’s Device

- 6Design and Documentation Support

- 7About the Author

5.2 Latency

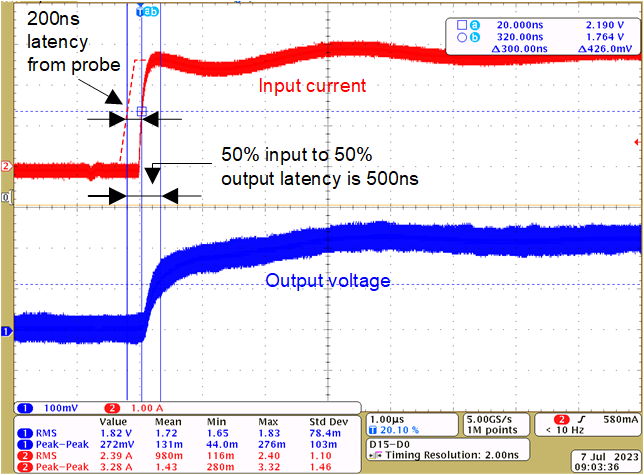

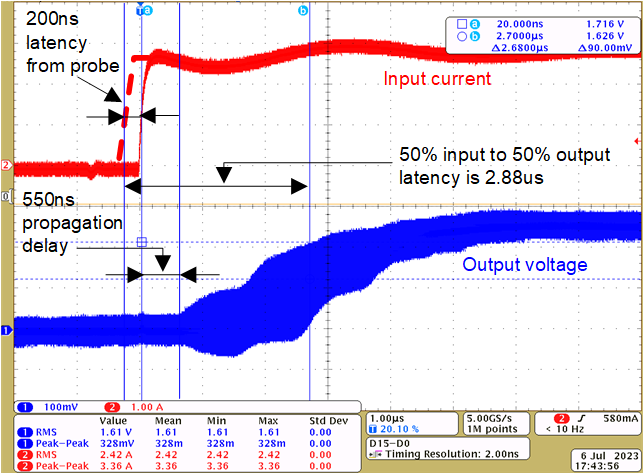

For the latency test details, see Section 4.4.2.2. Inject a 10kHz, 3A peak square wave current into TIDA-010937 and measure the latency between 50% input and 50% output. The test results are shown in Figure 5-1 and Figure 5-2

Figure 5-1 Latency Test

(TMCS1123B3)

Figure 5-1 Latency Test

(TMCS1123B3) Figure 5-2 Latency Test (Competitor’s

Device)

Figure 5-2 Latency Test (Competitor’s

Device)Figure 5-1 shows TMCS1123 has a significant advantage on latency. The latency as low as 300ns provides the higher frequency current sensing and does not influence the system control bandwidth. For the competitor’s device, the latency consists of two parts: one is up to 550ns propagation delay, the other is zero to 50% latency which is around 2.1μs.

Also, the persistence mode of the scope shows that there is large ringing during the rising edge of the input current on competitor’s device, while the output voltage of the TMCS1123 is smoother and is designed for high di/dt applications.