TIDUF82A August 2024 – November 2024 DRV8162 , INA241A , ISOM8710

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

-

2System Overview

- 2.1 Block Diagram

- 2.2 Design Considerations

- 2.3 Highlighted Products

- 3Hardware, Software Test Requirements and Test Results

- 4Design and Documentation Support

- 5About the Authors

- 6Revision History

3.3.1.1 Power Up

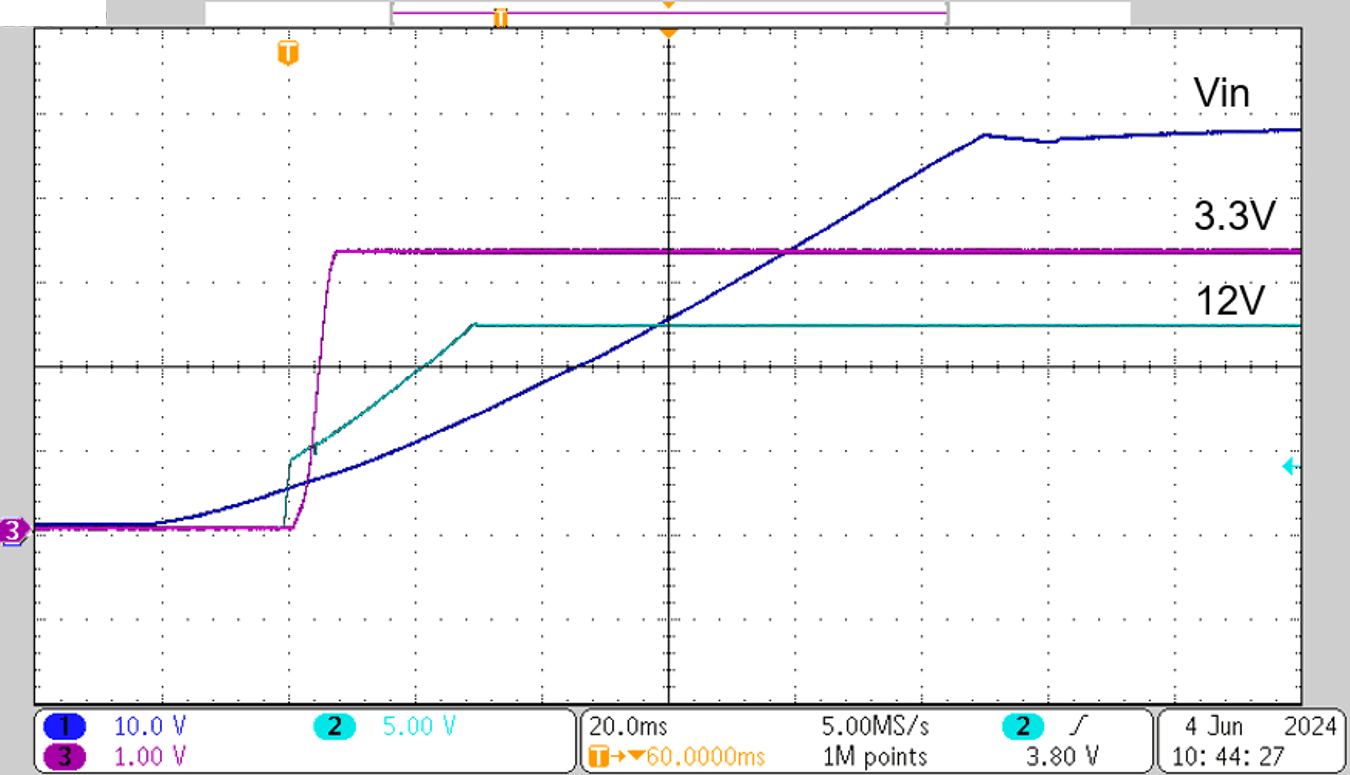

Figure 3-4 illustrates the TIDA-010956 power-up sequence.

Figure 3-4 TIDA-010956 Power-Up

Sequence

Figure 3-4 TIDA-010956 Power-Up

SequenceThe power up sequence of the system is as follows: 48V VIN (CH1 in dark blue) goes above approximately 5V first, then LMR38010FDDAR starts providing the 12V rail (CH2 in light blue). When this 12V rail is approximately 5V, the 3.3V rail (CH3 in purple) is enabled.

The VIN has a slow ramp up while charging the VDC bus capacitors which are mainly of 330µF × 2 + 2.2µF × 20 and sum up to over 700µF. Another 180µF × 20 = 3.6mF needs to be added if a capacitor board is adopted.