JAJSPZ6F May 2002 – March 2023 SN65HVD05 , SN65HVD06 , SN65HVD07 , SN75HVD05 , SN75HVD06 , SN75HVD07

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 Recommended Operating Conditions

- 5.3 Thermal Information

- 5.4 Package Dissipation Ratings

- 5.5 Driver Electrical Characteristics

- 5.6 Driver Switching Characteristics

- 5.7 Receiver Electrical Characteristics

- 5.8 Receiver Switching Characteristics

- 5.9 Typical Characteristics

- 6 Function Tables

- 7 Equivalent Input and Output Schematic Diagrams

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

3 概要

SN65HVD05、SN75HVD05、SN65HVD06、SN75HVD06、SN65HVD07、SN75HVD07 は、3 ステート差動ライン・ドライバと作動ライン・レシーバを組み合わせた製品です。これらは平衡データ転送用に設計されており、ANSI TIA/EIA-485-A および ISO 8482E 標準準拠のデバイスと相互運用が可能です。このドライバは、ノイズ・マージンを大きくするため、これらの規格で要求されている以上の差動出力電圧を供給できるよう設計されています。ドライバとレシーバはそれぞれアクティブ High、アクティブ Low のイネーブルを備えており、それらのイネーブルを外部で互いに接続することで、方向制御として機能させることができます。

ドライバ差動出力とレシーバ差動入力は内部で接続されており、差動入出力 (I/O) バス・ポートを形成しています。この設計により、ドライバが無効になったり、電力が供給されなくなっても、バスへの負荷が最小限になります。これらのデバイスは正負の同相電圧範囲が広いため、パーティライン・アプリケーションに適しています。

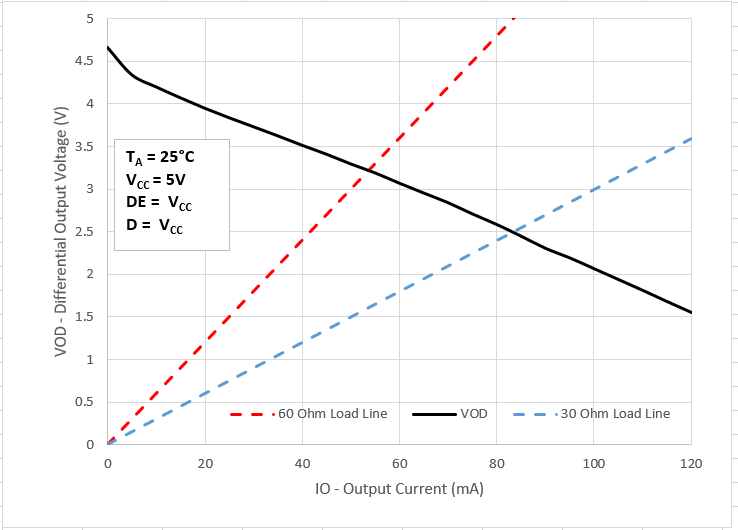

図 3-1 差動出力電圧と差動出力電流との関係

図 3-1 差動出力電圧と差動出力電流との関係