JAJSTH6M July 1999 – March 2024 SN65LVDS1 , SN65LVDS2 , SN65LVDT2

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 デバイスのオプション

- 5 ピン構成および機能

- 6 仕様

- 7 パラメータ測定情報

- 8 詳細説明

- 9 アプリケーションと実装

- 10電源に関する推奨事項

- 11レイアウト

- 12デバイスおよびドキュメントのサポート

- 13改訂履歴

- 14メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- D|8

- DBV|5

サーマルパッド・メカニカル・データ

発注情報

11.1.1 マイクロストリップとストリップラインのトポロジ

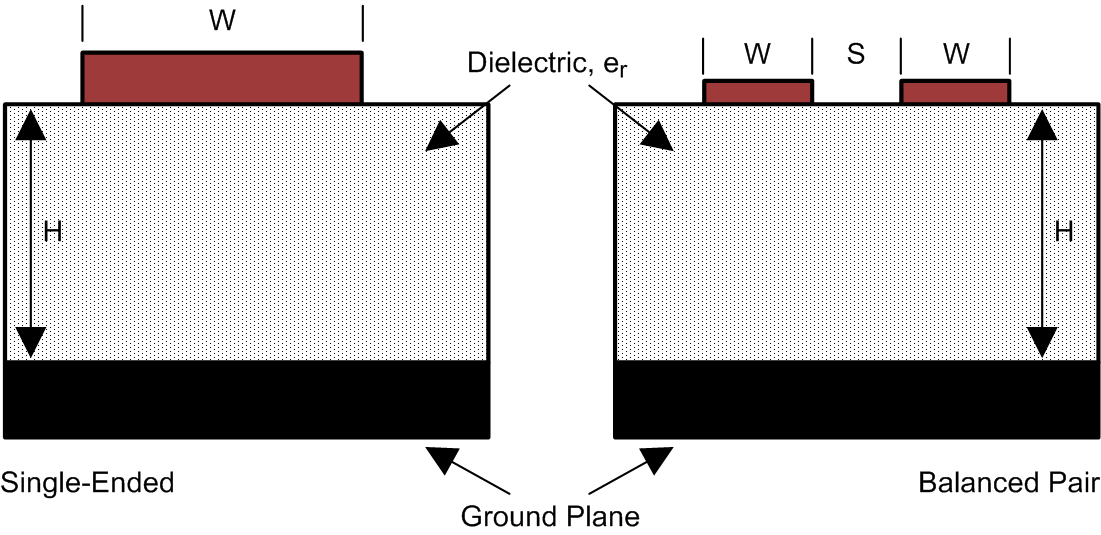

SLLD009 に従い、プリント基板には通常、2 つの伝送ラインのオプションが用意されています。マイクロストリップとストリップラインです。マイクロストリップは、図 11-1 に示すように、PCB の外層のパターンです。

図 11-1 マイクロストリップのトポロジ

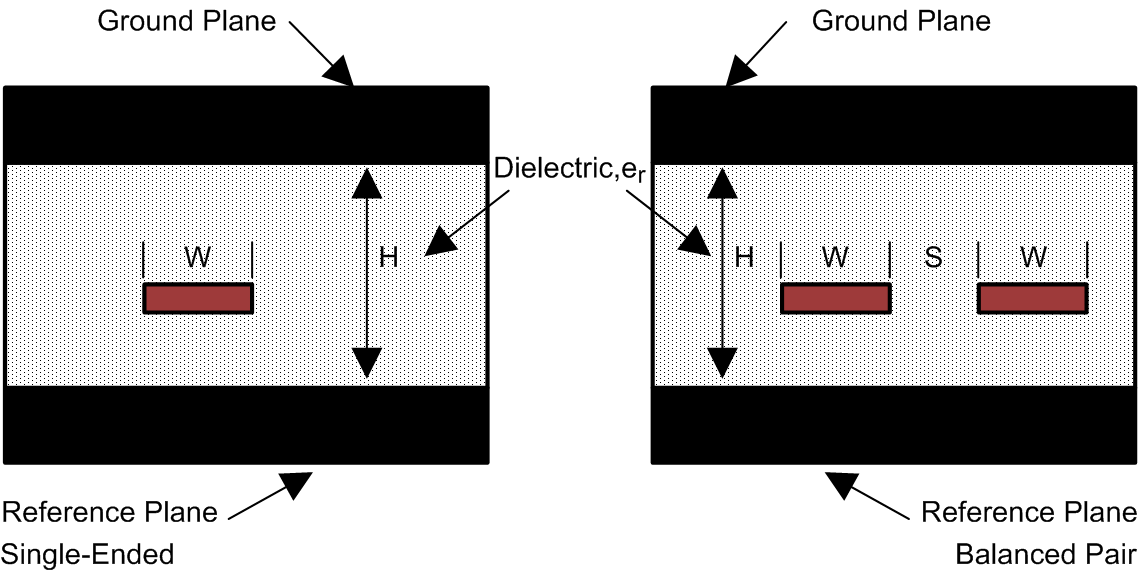

図 11-1 マイクロストリップのトポロジ一方、ストリップラインは 2 つのグランド プレーン間のパターンです。ストリップラインは、基準プレーンが埋め込まれたパターンを効果的にシールドするため、放射と外部からの影響に関する問題を受けにくくなります。ただし、高速伝送を考えると、2 つのプレーンを並べて使用すると、静電容量が増加します。可能であれば、LVDS 信号がマイクロストリップ伝送ラインを通るようにすることを推奨します。PCB パターンを使用すると、全体のノイズ バジェットと反射許容量に基づいて、ZO に必要な公差を指定できます。脚注 11、22、33 に、差動およびシングルエンド パターンの ZO および tPD の式を示します。 (2)(3)(4)

図 11-2 ストリップラインのトポロジ

図 11-2 ストリップラインのトポロジ2. Howard Johnson & Martin Graham.1993. High Speed Digital Design – A Handbook of Black Magic Prentice Hall PRT. ISBN number 013395724.

3. Mark I. Montrose. 1996.Printed Circuit Board Design Techniques for EMC Compliance IEEE Press. ISBN number 0780311310.

4. Clyde F. Coombs, Jr. Ed, Printed Circuits Handbook, McGraw Hill, ISBN number 0070127549.