JAJSGX8C April 2002 – February 2019 SN65LVDT14 , SN65LVDT41

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Receiver Electrical Characteristics

- 7.6 Driver Electrical Characteristics

- 7.7 Device Electrical Characteristics

- 7.8 Receiver Switching Characteristics

- 7.9 Driver Switching Characteristics

- 7.10 Typical Characteristics

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- PW|20

サーマルパッド・メカニカル・データ

発注情報

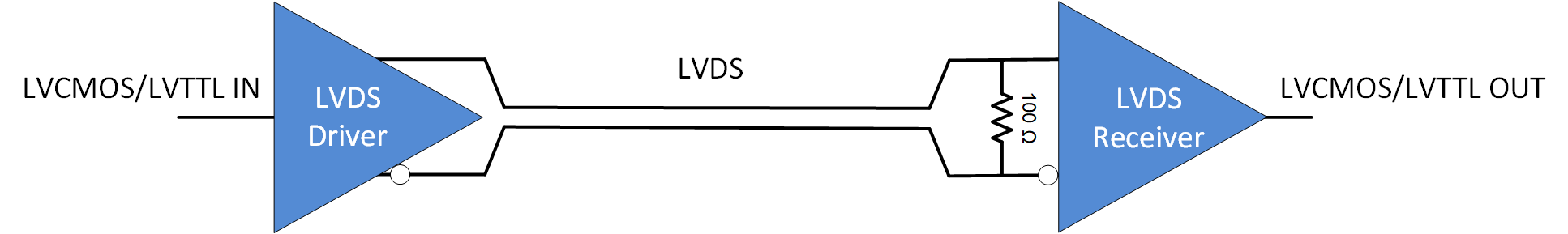

10.2 Typical Application

Point-to-Point applications provide a clean signaling environment for the fast edge rates of the SN65LVDTxx and other LVDS components. The SN65LVDTxx is connected through a balanced media which may be a standard twisted-pair cable, a parallel pair cable, or simply PCB traces to a LVDS receiver. Typically, the characteristic differential impedance of the media is in the range of 100 Ω. The SN65LVDTxx device is intended to drive a 100-Ω transmission line. The 100-Ω termination resistor is selected to match the media and is located as close to the LVDS receiver input pins as possible.

Figure 19. Typical LVDS Point-to-Point Application

Figure 19. Typical LVDS Point-to-Point Application