JAJA564B January 2018 – September 2024 ADS7040 , ADS7041 , ADS7042 , ADS7056 , ISOTMP35 , ISOTMP35-Q1

設計の説明

この設計書では、センサ出力をSAR ADC入力に直接接続する方法を説明します。ワイヤレス環境センサ、ガス検知器、煙 / 熱感知器などの用途では、入力の変化が非常にゆっくりなので、センサ出力電圧のサンプリングも低速になります (10ksps 程度)。このようなシステムでは、設計の小型化 低コスト化のために、ドライバ アンプなしでセンサ出力をSAR ADC入力に直接接続できます。

センサ出力を SAR ADC に直接接続

以下の図は、ドライバ アンプなしでセンサをSAR ADC入力に直接接続する標準的アプリケーション図です。センサ ブロックは、センサ出力のテブナン等価回路となっています。電圧源 VTH はテブナン等価電圧で、ソース抵抗 RTH はテブナン等価インピーダンスです。大半のセンサ データシートには、センサのテブナン モデルが記載されており、これにより直列インピーダンスの値を簡単に計算できます。

仕様

| パラメータ | 計算結果 | シミュレーション結果 | 測定結果 |

|---|---|---|---|

| ADC過渡入力電圧セトリング誤差 | < 0.5LSB < 100.5µV |

36.24µV | 該当なし |

| ステップ入力フルスケール範囲 | 3.15 V | 3.15 V | 3.14978 |

| 入力ソース インピーダンス (RTH) | 10kΩ | 10kΩ | 10.01kΩ |

| フィルタ コンデンサ値 (CFLT) | 680pF | 680pF | 該当なし |

| ADCサンプリング速度 | 10ksps | 10ksps | 10ksps |

デザイン ノート

- 入力信号のソース インピーダンスを特定します。入力ソース インピーダンスとフィルタ コンデンサ(既知の値)のRC時定数を計算します。

- 所定のソース インピーダンスとフィルタ コンデンサの組み合わせで入力信号が安定化するのに必要な最小アクイジション時間を特定します。

- 歪みを最小限に抑えるために、COGコンデンサを選定します。

- 適切なゲイン ドリフトを実現し、歪みを最小限に抑えるために、0.1% 20ppm/℃以下の薄膜抵抗を使用します。

ADC 入力セトリング用の部品選定

アナログ入力ソースに、SAR ADCのスイッチト キャパシタ負荷を駆動し、SAR ADCのアクイジション時間内にアナログ入力信号をLSBの1/2以内にセトリングする能力があれば、SAR ADCをセンサに直接接続できます。これを実現するには、外付け RC フィルタ (RTH と CFLT) が ADC のアクイジション時間 (tACQ) 内に安定化する必要があります。ADCアクイジション時間と外付けフィルタのRC時定数の関係は次のとおりです。

ここで、

- ԎFLT = RTH × CFLT

- kはNビットADCの単極時定数です。

次の設計例の値はp.1の表に記載されています。

K = 11 (14 ビット ADC の単極時定数乗数) – 詳細については、『アナログ エンジニアのポケット リファレンス ガイド』e-Book の p.96 および p.97 を参照してください。

次の式を用いて適切なセトリングに必要な最小アクイジション時間を計算します。

SAR ADC と SAR ADC 用フロント エンド設計の詳細については、『Introduction to SAR ADC Front-End Component Selection』ビデオを参照してください。

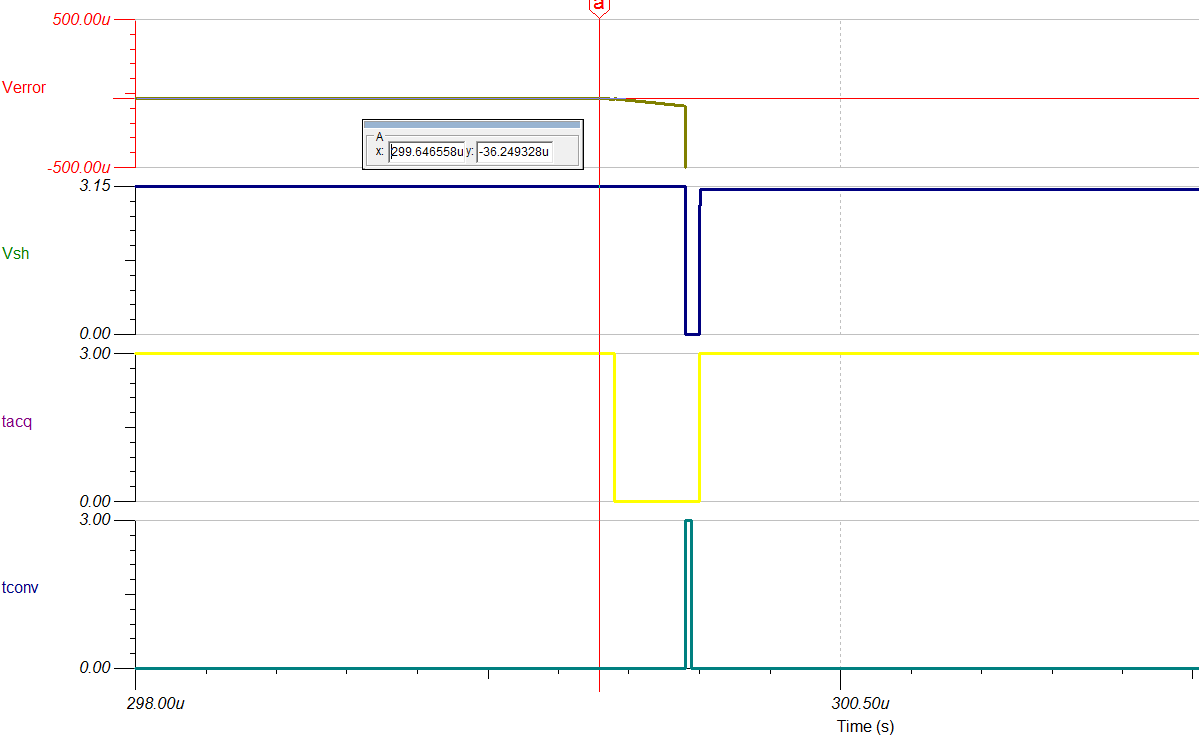

TI-TINA を使用した過渡入力電圧セトリング シミュレーション

以下の図は、3.15V の DC 入力信号を受け取った ADS7056 ADC のセトリングを示しています。このようなシミュレーションは、サンプル/ホールド キックバック回路が適正に選定されていることを示します。この件の詳しい理論については、『TI Precision Labs - ADCs』トレーニング ビデオ シリーズの『Refine the Rfilt and Cfilt Values』を参照してください。

入力信号セトリングのために SAR ADC のアクイジション時間を延長

次の方法でスループットを下げることにより、SAR ADCのアクイジション時間を延長できます。

- SCLKの周波数を下げることによってスループットを下げる。

- SCLKを最高許容値に固定し、CSのHIGH時間を延長する。

以下の表に、10ksps のスループットで動作する ADS7056 SAR ADC における上記 2 つのケースのアクイジション時間を示します (tcycle = 100µs)。ケース2のほうが、SCLK周波数が上がって変換/サイクル時間が固定されるため、入力信号が安定化できるアクイジション時間は長くなっています。

| ケース | SCLK | tcycle | 変換時間 (18 × tSCLK ) | アクイジション時間 (tcycle - tconv ) |

|---|---|---|---|---|

| 1 | 0.24MHz | 100µs | 74.988µs | 25.01µs |

| 2 | 60MHz | 100µs | 0.3µs | 99.70µs |

以下の表は、出力インピーダンス10kΩのセンサ出力をADC入力に直接接続したときの8ビット、10ビット、12ビット、14ビットのADCのサンプリング速度と有効ビット数(ENOB)に関する性能比較を示しています。予想どおり、サンプリング レートが上がるほどアクイジション時間は短くなるため、ENOBは減少します。

| サンプリング速度(ksps) | ADS7040 (8 ビット ADC) ENOB (RTH = 10kΩ、 CFLT = 1.5nF) |

ADS7041 (10 ビット ADC) ENOB (RTH = 10kΩ、 CFLT = 1.5nF) |

ADS7042 (12 ビット ADC) ENOB (RTH = 10kΩ、 CFLT = 1.5nF) |

ADS7056 (14 ビット ADC) ENOB (RTH = 10kΩ、CFLT = 680pF) |

|---|---|---|---|---|

| 10 | 7.93 | 9.87 | 10 | 12.05 |

| 100 | 7.92 | 9.85 | 9.97 | 10.99 |

| 500 | 7.88 | 9.68 | 9.95 | 8.00 |

さまざまなスループット レート、さまざまなソース インピーダンスで達成される性能

以下の図は、さまざまなスループット、さまざまな入力インピーダンスでADS7056により達成されるENOBを示しています。なお、以下のグラフの結果は、いずれもアナログ入力信号を100Hzとし、ADCドライバ アンプなしで取得しました。

使用デバイス

| デバイス | 主な特長 | リンク | 類似デバイス |

|---|---|---|---|

| ADS7040 | 分解能: 8ビット、SPI、サンプル レート: 1Msps、シングルエンド入力、AVDD/Vref入力電圧範囲: 1.6V~3.6V | 超低消費電力、超小型サイズ SAR ADC、8 ビット、1MSPS、シングルエンド | A/D コンバータ (ADC) |

| ADS7041 | 分解能 10ビット、SPI、サンプル レート 1Msps、シングルエンド入力、AVDD/Vref 入力電圧範囲 1.6V~3.6V | 超低消費電力、超小型サイズ SAR ADC、10 ビット、1MSPS、シングルエンド | |

| ADS7042 | 分解能: 12ビット、SPI、サンプル レート: 1Msps、シングルエンド入力、AVDD/Vref入力電圧範囲: 1.6V~3.6V | SPI 搭載、12 ビット、1MSPS、超低消費電力、超小型サイズ SAR ADC | |

| ADS7056 | 分解能: 14ビット、SPI、サンプル レート: 2.5Msps、シングルエンド入力、AVDD/Vref入力電圧範囲: 1.6V~3.6V | SPI 搭載、14 ビット、2.5MSPS、超低消費電力、超小型サイズ SAR ADC |

ADS7042およびADS7056はAVDDを基準入力電圧として使用します。TPS7A47などの高PSRR LDOを電源として使用する必要があります。

主要なファイルへのリンク

テキサス・インスツルメンツ、SBAA256 用のソース ファイル、SBAC178 サポート ファイル