JAJSVH1A April 2003 – October 2024 UC2842AQ , UC2843AQ , UC2845AQ

PRODUCTION DATA

4 ピン構成および機能

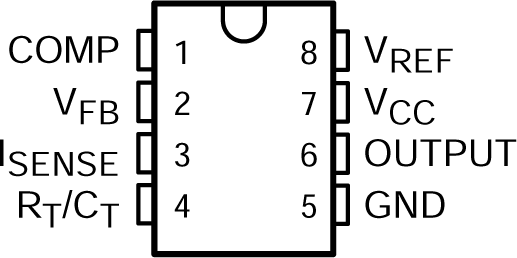

図 4-1 D 8 ピン パッケージ (上面図)

図 4-1 D 8 ピン パッケージ (上面図)表 4-1 ピンの機能

| ピン | 種類 (1) | 説明 | |

|---|---|---|---|

| 名称 | 番号 | ||

| COMP | 1 | O | 低インピーダンスの 1MHz 内部エラー アンプを出力します。このアンプは、ピーク電流制限または PWM コンパレータへの入力でもあり、開ループ ゲイン (AVOL) は 90dB です。このピンは最大 6mA をシンクでき、内部的に電流が制限されていません。 |

| VFB | 2 | I | エラー アンプへの入力。パワー コンバータの電圧帰還ループを制御して安定性を確保するために使用できます。 |

| ISENSE | 3 | I | 本コントローラのピーク電流制限機能 (PWM コンパレータ) の入力。電流検出抵抗と組み合わせて使用する場合、エラー アンプの出力電圧によって、電源システムのサイクル単位のピーク電流制限が制御されます。最大ピーク電流検出信号は、内部で 1V にクランプされます。「機能ブロック図」を参照してください。 |

| RT/CT | 4 | I | 外部タイミング抵抗 (RT) とタイミング コンデンサ (CT) を使用してプログラムされる。内部発振器への入力。これらのタイミング部品の適切な選択については、「発振器」を参照してください。470pF~4.7nF の容量値を使用することをお勧めします。また、タイミング抵抗には 5kΩ~100kΩ の値を選択することをお勧めします。 |

| GND | 5 | GND | コントローラ信号グランド。 |

| 出力 | 6 | O | 1A トーテムポール ゲート ドライバの出力。このピンは、最大 1A のゲート ドライバ電流をシンクおよびソースできます。ゲート ドライバ電流を制限するには、ゲート ドライバ抵抗を使用する必要があります。 |

| VCC | 7 | I |

デバイスに電力を供給するアナログ コントローラ バイアス入力。合計 VCC 電流は、静止 VCC 電流と平均 OUTPUT 電流の和です。スイッチング周波数と MOSFET ゲート電荷 Qg が判明していれば、平均 OUTPUT 電流は次の式で計算できます。 IOUTPUT = Qg × fSW このピンには、最小のパターン長でグランドに直接接続されたバイパス コンデンサ (通常 0.1μF) が必要です。VCC にも、設計で使用するメイン スイッチング FET のゲート容量の 10 倍以上のバイパス コンデンサを追加する必要があります。 |

| VREF | 8 | O | ゲート ドライバへのバイアス入力。このピンには、設計で使用するメイン スイッチング FET のゲート容量の 10 倍より大きいバイアス コンデンサが必要です。 |

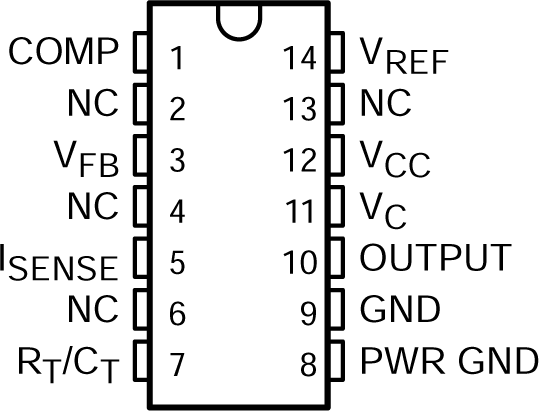

図 4-2 D 14 ピン パッケージ (上面図)

図 4-2 D 14 ピン パッケージ (上面図)表 4-2 ピンの機能

| ピン | 種類 (1) | 説明 | |

|---|---|---|---|

| 名称 | 番号 | ||

| COMP | 1 | I/O | エラー アンプ補償ピン |

| NC | 2 | - | 接続しない |

| VFB | 3 | I | エラー アンプ入力 |

| NC | 4 | - | 接続しない |

| ISENSE | 5 | I | 電流検出コンパレータ入力 |

| NC | 6 | - | 接続しない |

| RT/CT | 7 | I/O | 発振器の RC 入力 |

| PWR GND | 8 | GND | 出力 PWM のグランド端子 |

| GND | 9 | GND | デバイス電源のグランド端子 |

| 出力 | 10 | O | PWM 出力 |

| VS | 11 | - | 出力 PWM の正電圧電源 |

| VCC | 12 | - | デバイスの正電源電圧 |

| NC | 13 | - | 接続しない |

| VREF | 14 | O | オシレータの電圧リファレンス |

(1) I = 入力、O = 出力、I/O = 入出力、GND = グランド。