JAJT289 August 2017 LMG3522R030 , UCD3138

マイクロプロセッサおよび ASIC (特定用途向け集積回路)には、低電圧、大電流の電源が必要です。これらの電源には通常、出力電圧の変動について、特に負荷過渡イベントに対して非常に厳格な要件が課されます。これらの電源をテストする際には、設計者にとって課題が発生する可能性があり、仕様に準拠していることを確認するのが困難な場合もあります。

Power Tip 63 では、負荷過渡テストに関連するいくつかの問題について Robert Kollman が解説しています。ここでは、それに追加する説明と、これらの困難な条件のテストを簡素化するために使用できる方法について説明します。

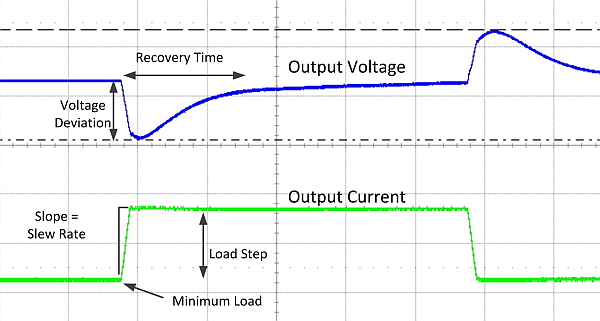

まず、電源を適切に設計するためには、すべての過渡仕様を理解すると同時に、これらがテストにどのように適用されるかを理解する必要があります。代表的な過渡仕様は次のとおりです。

- 負荷ステップの大きさをアンペア単位、または全負荷に対するパーセントで表した値。

- 過渡現象中の最小負荷 (ゼロの場合もあります)。

- 負荷ステップのスルーレート。通常、アンペア/μs 単位。

- ステップの両端で許容される最大電圧変動。

- 予想される復帰時間。

図 1 に、これらの仕様が通常どのように定義されるかの例を示します。

図 1 負荷過渡測定に関する図による説明

図 1 負荷過渡測定に関する図による説明すべての仕様を理解すれば、要件を満たすように電源を設計することができます。ただし、これらの要件をテストすることが課題になります。出力電圧が 1V、負荷ステップが 100A、スルーレートが 1,000A/μs という要件を見かけることは珍しくありません。ほとんどのテスト状況での制限要因は、テスト対象の電源と負荷の間のインダクタンスです。実際のシステムでは、多くの場合、電源は、電力供給先である負荷のすぐ隣に配置されるため、寄生インダクタンスは最小化されます。

対象となる電源の負荷過渡応答をテストするには、さまざまな方法を使用できます。それぞれに長所と短所があります。 ここでは、以下の選択肢を比較します。外部の電子回負荷、外部の過渡ボード、「FET (電界効果トランジスタ) スラマー」、オンボード過渡ジェネレータ、ソケット ベースの過渡テスタ。

外部の電子負荷は、過渡応答をテストするための最も一般的な方法であり、最も利便性が高いでしょう。ほとんどの負荷には、電流レベルと遷移時間を簡単に設定できるモードがあります。主な欠点は、外部配線または実際の負荷の制約によって、スルーレートが制限されることです。

外部の過渡ボードを使用すると、通常はスルーレートに関してより良好な結果が得られますが、フレキシビリティが犠牲になります。設計によっては、負荷過渡ボードは、最大電流、熱放散、またはスルーレートに制限がある場合があります。過渡ボードは外部で接続されているため、多くの場合、配線がスルーレートを制限するボトルネックになります。また、テストする電源装置ごとにボードを調整または構成する必要があります。

FET スラマーは、高速過渡の結果を得るための手早くて粗雑な方法です。MOSFET (metal-oxide semiconductor field-effect transistor) のドレインからソースへ向けて、抵抗を経由して、または直接、電源の出力の両端を接続します。ファンクション ジェネレータがゲートを制御します。外部配線は最小限なので、寄生インダクタンスは大幅に低減されます。

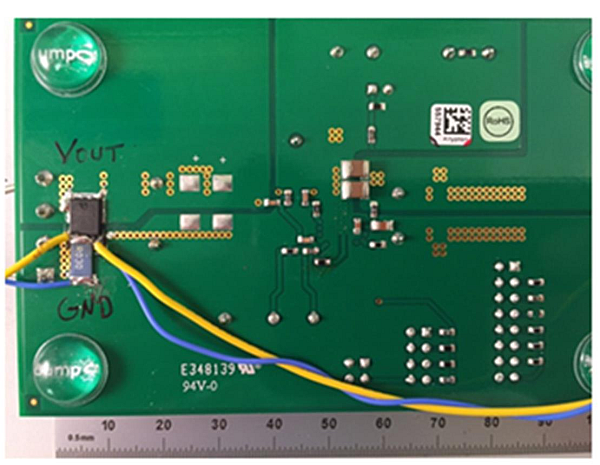

この方法は通常、高いスルーレートを生成できますが、テストの制御と再現性が困難な場合があります。プリント基板 (PCB) の変更が必要になることもあります (図 2)。この方法のもう 1 つの問題は、実際の負荷ステップ電流の測定が困難で、不正確になる可能性があることです。

図 2 FET スラマー付きの PCB の例

図 2 FET スラマー付きの PCB の例オンボードの過渡ジェネレータは、大電流の高速過渡の性能をテストする際に非常に役立ちます。正確な負荷過渡仕様を満たすように、回路を設計することができます。主な欠点は、余分なコストがかかること、部品がスペースを占有することです。さらに、複数の異なる測定を実施するフレキシビリティを得るのが困難であったり、時間を要する場合があります。

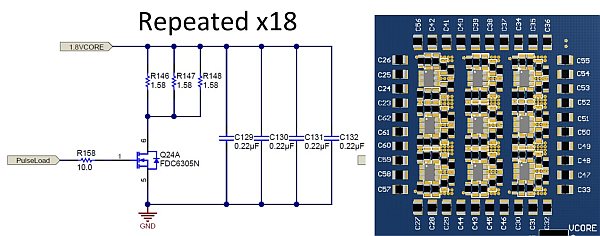

オンボードの過渡ジェネレータの設計もかなり複雑になる可能性があります。これは、抵抗と FET を 555 タイマで制御するようなシンプルなものもあれば、図 3 に示すような複雑なものもあります。より複雑な設計では、複数の段を設けて、より小型でより高速なスイッチング FET を使用します。この種の設計では、1,000A/μs のスルーレートを達成できます。

図 3 オンボード過渡ジェネレータのより複雑なバージョン

図 3 オンボード過渡ジェネレータのより複雑なバージョン最後の選択肢は、プロセッサ ソケットと専用の過渡テスタ ツールを使用することです。この選択肢は、ツール自体の価格が高い可能性があり、PCB もはるかに高価になるため、最も費用のかかる方法です。ただし、指定されたプロセッサ要件に対して最も正確な結果を得ることができます。プロセッサや ASIC のメーカーは多くの場合、これらのツールを開発しており、適切なテスト条件を満たす目的で専用に製作されています。

表 1 に、過渡テストの選択肢を示します。

| 方法 | 長所 | 短所 |

|---|---|---|

| 外部電子負荷 | シンプルでフレキシブル、追加コストなし | 外部接続が原因でスルーレートが制限される |

| 外部過渡ボード | シンプルで低コスト | テストごとに変更が必要。外部接続が原因でスルーレートが制限される |

| FET スラマー | 低コスト、高速スルーレート | 高性能のファンクション ジェネレータが必要。実際の電流の測定は困難かつ不正確になる可能性がある。制御が困難になる可能性がある |

| オンボード過渡ジェネレータ | 超高速スルーレート。テスト対象の電源専用に設計 | テスト条件が異なるごとに、基板に変更を加える必要が生じる。PCB 上で余分のスペースを占有。コスト増大の可能性。電流の測定が困難 |

| ソケット ベースの過渡テスタ | 正確な仕様準拠の確認に特化したテスト。テストを容易にするため、一般的にソフトウェアで制御 | 非常に高価。ソケットを実装するための PCB レイアウトが困難。 PCB は層数とソケット配置が原因で非常に高価になる可能性がある |

負荷過渡のテストは、電源の設計および仕様準拠にとって非常に重要な部分です。テスト装置の寄生インダクタンスは、目的のスルーレートを達成する能力に悪影響を及ぼす可能性があります。ここで説明した方法を使用して、この問題を回避できることを願っています。

過渡負荷の詳細については、 Power House ブログをご覧ください。電源のヒント:単純な回路で高速かつ制御可能な過渡負荷を生成。

その他の Power Tips については、 TI の Power Tips ブログ シリーズをご覧 ください。

関連項目:

- 電源のテスト

- 電圧レギュレータの負荷過渡応答テスト

- Power Tip 63:高 di/dt 電源のテスト

- Power Tips #78:フライバック電源のクロスレギュレーションを改善する同期整流器

- 扱いの難しい負荷に対応し、PSU の特性評価に貢献するパワー ドライバの設計

- 電力過渡バッファにより IC & 回路のテストを実現

- 過渡負荷により電源システムの問題点を検証

この記事は、以前 EDN.com で公開された記事です。