SLAAEI9 December 2023 MSPM0C1103 , MSPM0C1104 , MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3105-Q1 , MSPM0G3106 , MSPM0G3106-Q1 , MSPM0G3107 , MSPM0G3107-Q1 , MSPM0G3505 , MSPM0G3505-Q1 , MSPM0G3506 , MSPM0G3506-Q1 , MSPM0G3507 , MSPM0G3507-Q1 , MSPM0L1105 , MSPM0L1106 , MSPM0L1228

- 1

- Abstract

- Trademarks

- 1MSPM0 Portfolio Overview

-

2Ecosystem And Migration

- 2.1 Ecosystem Comparison

- 2.2 Migration Process

- 2.3 Example

- 3Core Architecture Comparison

- 4Digital Peripheral Comparison

- 5Analog Peripheral Comparison

2.1.4 Debug Tools

STM support single wire interface module (SWIM) and debug module (DM). In-circuit debugging mode or in-circuit programming mode are managed through a single wire hardware interface featuring ultrafast memory programming. Coupled with an in-circuit debugging module, it also offers a non-intrusive emulation mode, making the in-circuit debugger extremely powerful, close in performance to a full-featured emulator. Besides, the typical debugger of STM8 is ST-LINK. The SWIM and JTAG/serial wire debugging (SWD) interfaces are used to communicate with any STM8 microcontroller located on an application board.

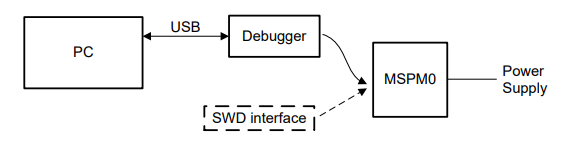

For MSPM0, the debug subsystem (DEBUGSS) interfaces the serial wire debug (SWD) two-wire physical interface to multiple debug functions within the device. MSPM0 devices support debugging of processor execution, the device state, and the power state (via EnergyTrace technology). For more details on the connection of the debugger, see Figure 2-5.

Figure 2-5 MSPM0 Debugging

Figure 2-5 MSPM0 DebuggingMSPM0 support XDS110 and J-Link debugger for standard serial wire debug.

The Texas Instruments XDS110 is for TI embedded processors. XDS110 connects to the target board using a TI 20-pin connector (adapters are available for TI 14-pin and Arm 10-pin and 20-pin connectors) and to the host PC using USB2.0 High Speed (480 Mbps). The XDS110 supports a wider variety of standards (IEEE1149.1, IEEE1149.7, SWD) in a single unit. All XDS debug probes support Core and System Trace in all Arm and DSP processors that feature an Embedded Trace Buffer (ETB). For details, see XDS110 Debug Probe.

J-Link debug probes are the most popular choice for optimizing the debugging and flash programming experience. Benefit from record-breaking flash loaders, up to 3-MiB/s RAM download speed and the ability to set an unlimited number of breakpoints in the flash memory of MCUs. J-Link also supports a wide range of CPUs and architectures included CortexM0+. For details, see the J-Link Debug Probes page.

Table 2-5 shows a different feature summery between XDS110 and J-LINK debugger supporting MSPM0.

| Features | XDS110 | XDS110 OB (1) | J-Link | |

|---|---|---|---|---|

| cJTAG (SBW) | √ | √ | √ | |

| BSL (2) tool | √ | √ | ||

| Backchannel UART | √ | √ | 2.5G (µVision V5.37.0) | |

| Power supply | 1.8 - 3.6 V | 3.3/5 V | 5 V | |

| IDE (3): CCS | √ | √ | √ | |

| IDE: 3rd party (4) | IAR/Keil | IAR/Keil | IAR/Keil | |