SNAA386 November 2023 CDCE6214 , CDCE6214-Q1 , CDCE6214Q1TM , LMK00301 , LMK00304 , LMK00306 , LMK00308 , LMK00334 , LMK00334-Q1 , LMK00338 , LMK03318 , LMK03328 , LMK3H0102 , LMK6C , LMK6H , LMKDB1104 , LMKDB1108 , LMKDB1120 , LMKDB1202 , LMKDB1204

5.1.3 PNA Measurement Result, With SSC

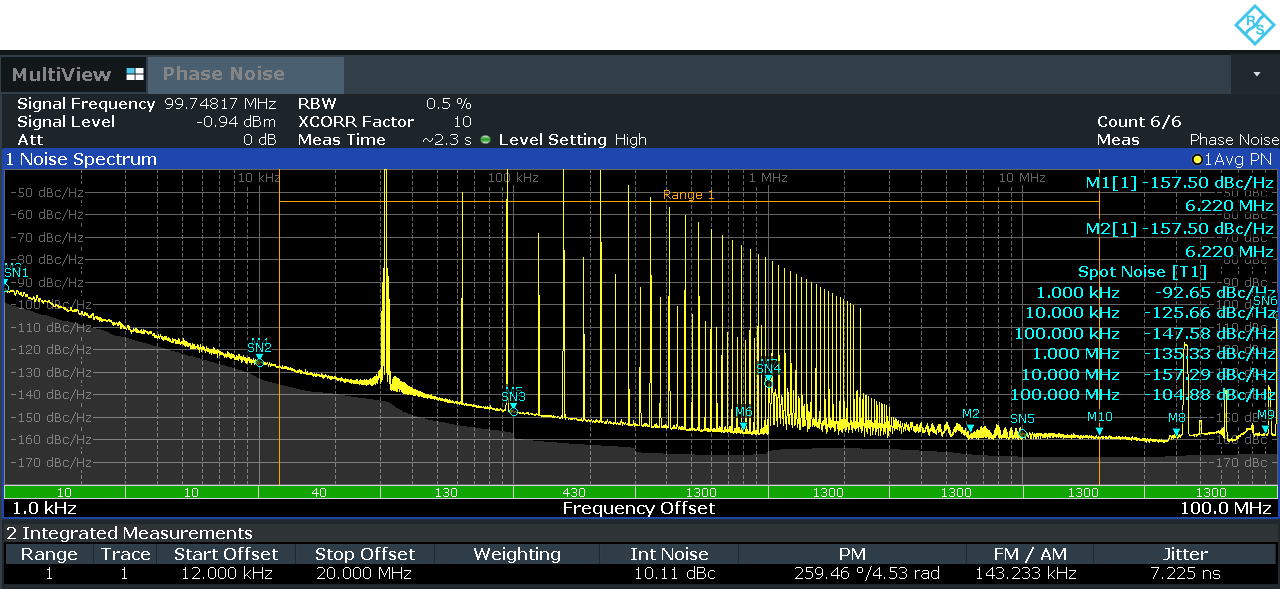

Figure 5-3 is the phase noise plot of the LMK3H0102 output clock as measured by the PNA when SSC is enabled. The SSC is configured for –0.5% down-spread modulation. The 12 kHz to 20 MHz phase jitter is higher as SSC adds jitter, but much of this is filtered out when applying the PCIe filters. For CCS and SRIS, spurs from the fundamental frequency and harmonics are removed only up to 2 MHz. This is done to minimize removal of non-SSC related spurs.

Figure 5-3 LMK3H0102 Phase Noise with

SSC

Figure 5-3 LMK3H0102 Phase Noise with

SSC