SNAA386 November 2023 CDCE6214 , CDCE6214-Q1 , CDCE6214Q1TM , LMK00301 , LMK00304 , LMK00306 , LMK00308 , LMK00334 , LMK00334-Q1 , LMK00338 , LMK03318 , LMK03328 , LMK3H0102 , LMK6C , LMK6H , LMKDB1104 , LMKDB1108 , LMKDB1120 , LMKDB1202 , LMKDB1204

5.1.1 PNA Measurement Result without SSC

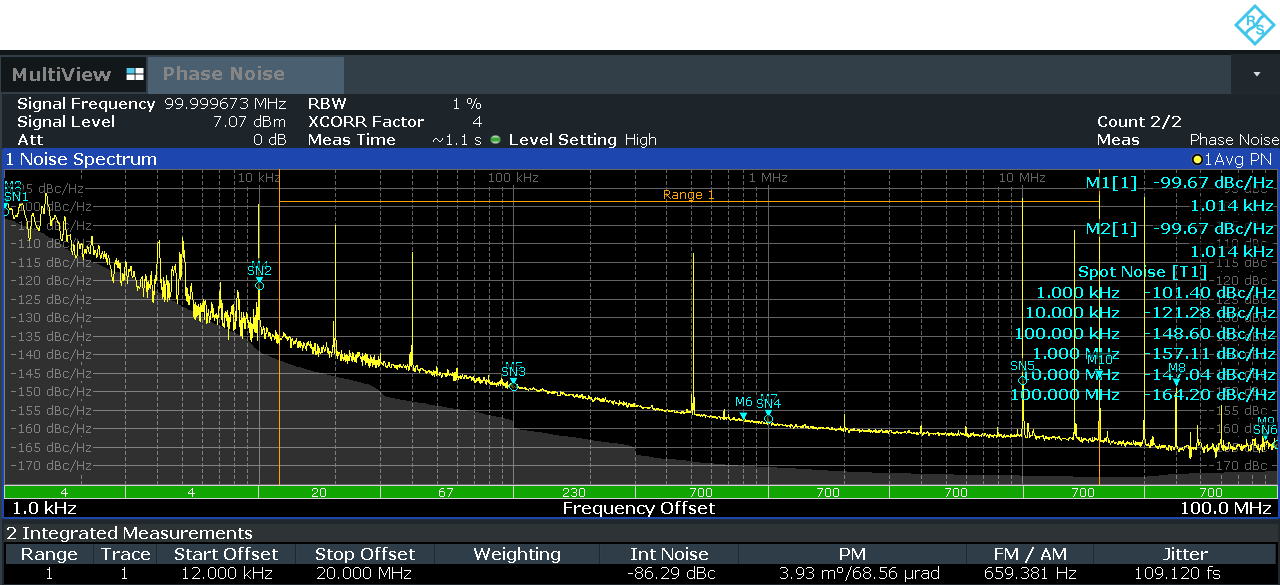

Figure 5-5 is the phase noise plot of the LMK3H0102 output clock as measured by the PNA. The 12 kHz to 20 MHz phase jitter is measured to be 179 fs. The PNA measurement is exported as a text file, from which we can import into the Texas Instruments PCIe Reference Clock Analysis Tool in TICS Pro. As PCIe Gen 6.0 requires data from 10 kHz to 50 MHz, the tool estimates the noise floor and extends the data to a full Nyquist band, 50 MHz.

Figure 5-2 LMK3H102 Phase Noise Without

SSC

Figure 5-2 LMK3H102 Phase Noise Without

SSC