SNLA435A September 2023 – January 2024 DS320PR1601 , DS320PR410 , DS320PR810

4.2 Eye Scan Application: System

Eye Scan can also be leveraged to gain insight into the vertical eye quality at the redriver’s transmitter in a PCIe system configuration. However, one must note that a PCIe redriver is best designed to handle pre-channel insertion loss, but in many system configurations, post-channel insertion loss is also present. Thus, Eye Scan vertical eye quality measurements can differ from vertical eye opening results shown with lane margining at the receiver (either at the root complex or at the endpoint).

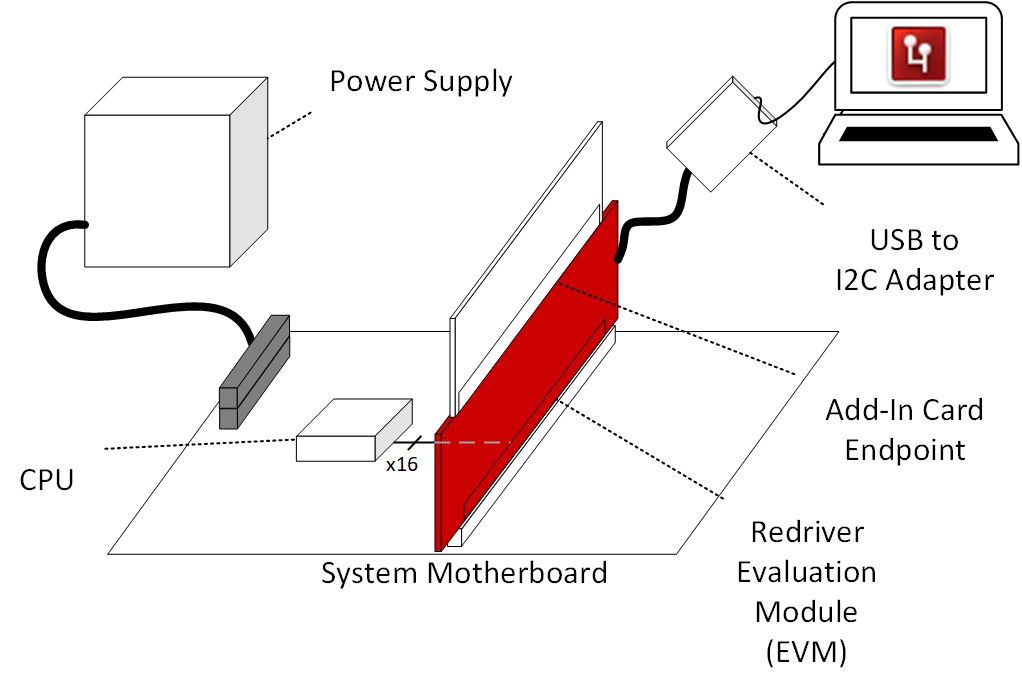

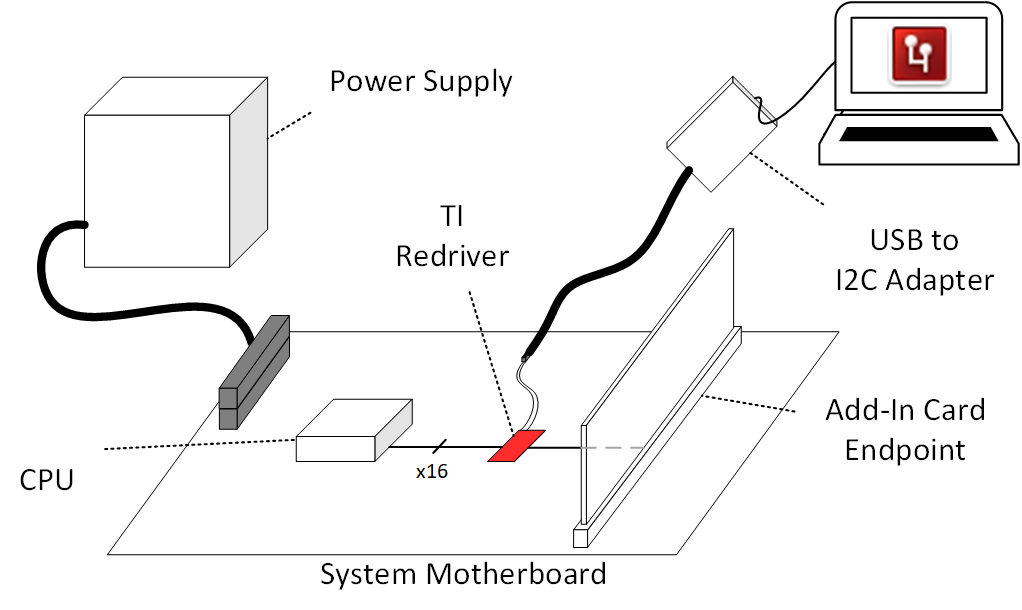

A typical PCIe system configuration utilizing a redriver encompasses either of the following two setups. Figure 4-3 details a system configuration using a Texas Instruments PCIe redriver on a TI EVM, while Figure 4-4 details a system configuration using a Texas Instruments PCIe redriver on a system motherboard.

Figure 4-3 PCIe System Configuration Using a TI PCIe Redriver EVM

Figure 4-4 PCIe System Configuration Using a TI PCIe Redriver on a Motherboard

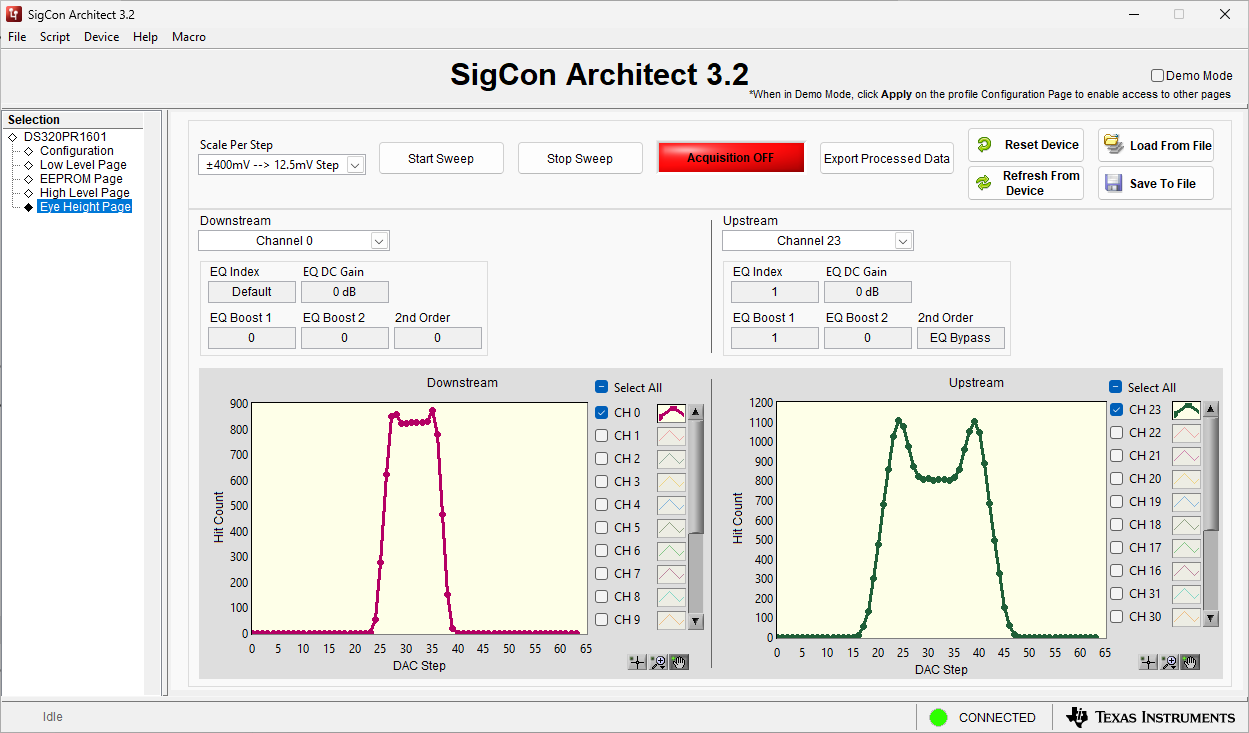

In each system configuration, Eye Scan can be utilized to provide insight on vertical eye quality at the redriver’s transmitter, which can help find a range of EQ boost settings that improve PCIe eye performance (in addition to PCIe lane margining tools). To better visualize an example of Eye Scan in a system configuration, an Eye Scan plot for one Downstream and one Upstream PCIe channel in the SigCon Architect GUI can be seen in Figure 4-5 during an active PCIe Gen4 link-up.

Figure 4-5 Example System Eye Scan Plot in the SigCon Architect GUI