SPRADE9 November 2023 AM2431 , AM2432 , AM2434 , AM623 , AM625 , AM625-Q1 , AM625SIP , AM62A3 , AM62A3-Q1 , AM62A7 , AM62A7-Q1 , AM62P-Q1 , AM6411 , AM6412 , AM6421 , AM6422 , AM6441 , AM6442 , AM6526 , AM6528 , AM6546 , AM6548 , AM67 , AM67A , AM68 , AM68A , AM69 , AM69A , DRA821U , DRA821U-Q1 , DRA829J , DRA829J-Q1 , DRA829V , DRA829V-Q1

4.2 Transmit Timing

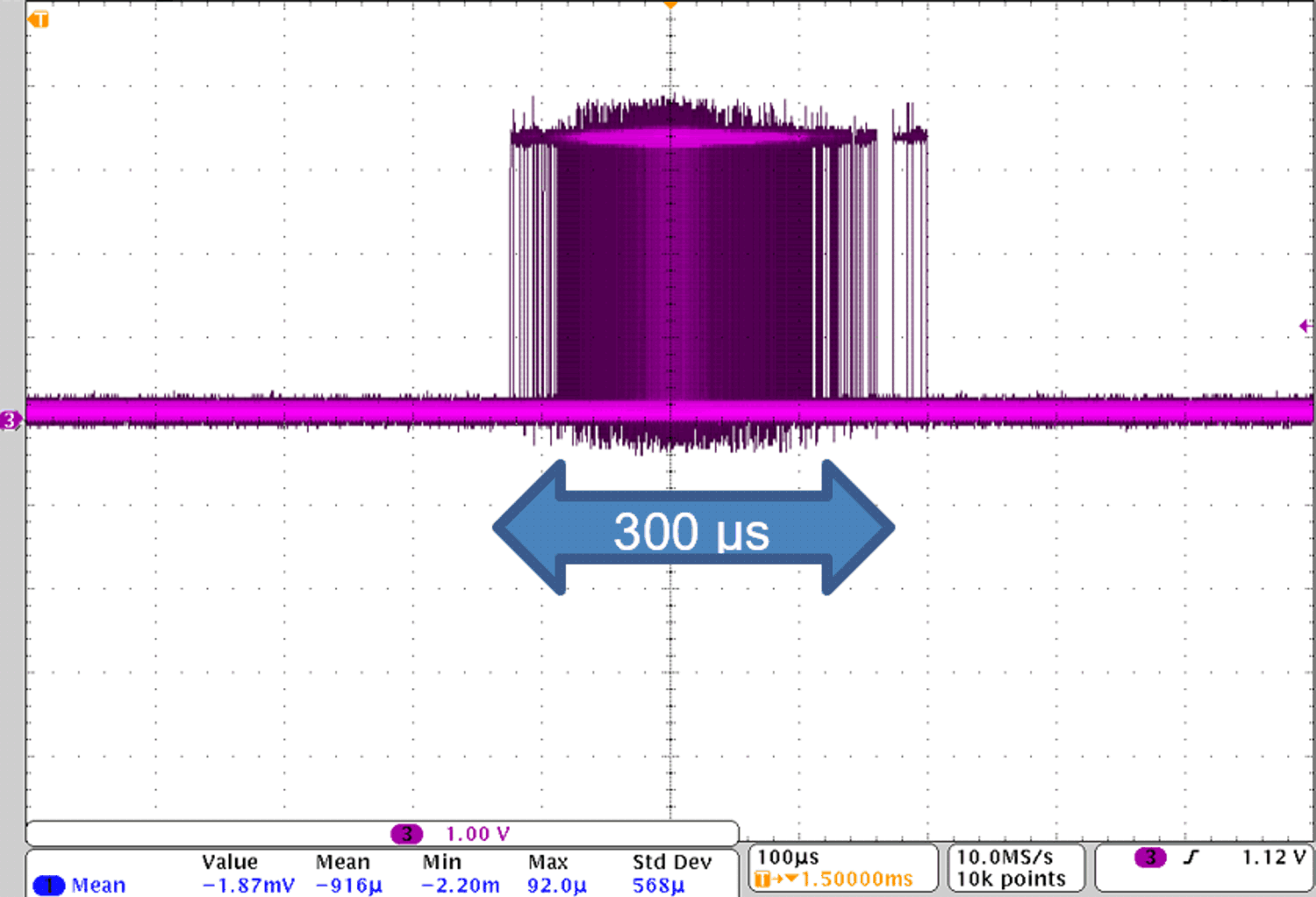

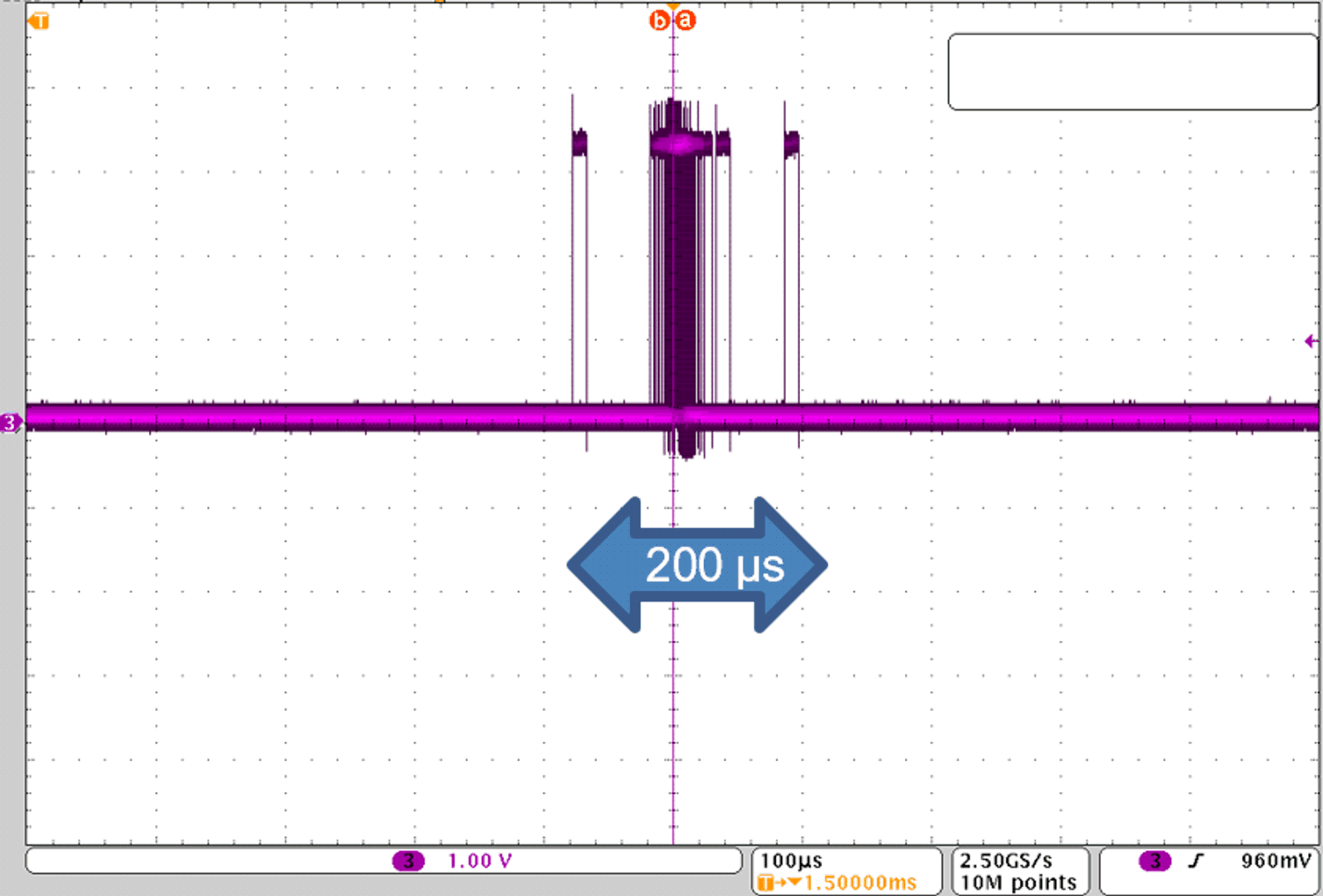

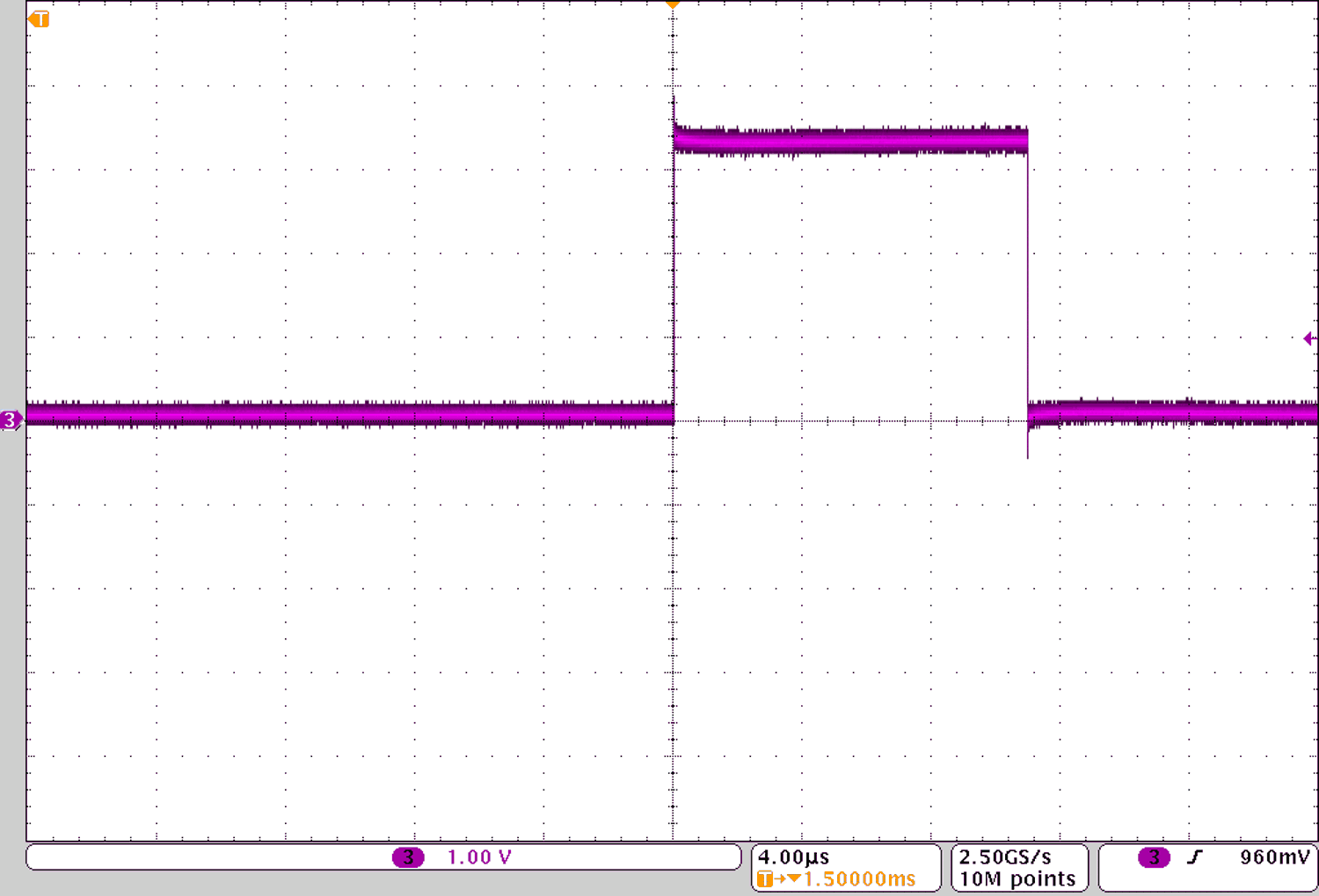

The timing of a Sitara AM6412 running on RT Linux with Codesys EtherCAT Main without any tuning or optimization is shown in Figure 4-2. The measurement is based on the TX_EN RGMII signal, which will be high from the beginning to the end of the frame. The signal stays high for the duration of transmitting the frame. For example, the duration of TX_EN RGMII signal at high level for a 200 byte frame at 100 Mbit/s EtherCAT is 16 μs. Jitter measurements needs to be accounted in the TX_EN measurement. The cycle time used is 1.5 ms, and the jitter of the start of the frames being placed on the wire is about ±120 μs. On the AM682 with 2 GHz Cortex A72 the same test in Figure 4-3 shows about half of that jitter.

Figure 4-2 Baseline CODESYS on Sitara AM6412

TX_EN Timing of EtherCAT Frames - 1.5 ms Cycle Time, Oscilloscope in Persistence

Mode

Figure 4-2 Baseline CODESYS on Sitara AM6412

TX_EN Timing of EtherCAT Frames - 1.5 ms Cycle Time, Oscilloscope in Persistence

Mode Figure 4-3 Baseline Codesys on Sitara AM682

TX_EN Timing of EtherCAT Frames - 1.5 ms Cycle Time, Oscilloscope in Persistence

Mode

Figure 4-3 Baseline Codesys on Sitara AM682

TX_EN Timing of EtherCAT Frames - 1.5 ms Cycle Time, Oscilloscope in Persistence

ModeFigure 4-4 shows a wireshark capture of the traffic on the Ethernet wire for the same use case on the AM6412.

Figure 4-4 Baseline Codesys on Sitara AM6412

Wireshark Capture of EtherCAT Frames - 1 ms Cycle Time

Figure 4-4 Baseline Codesys on Sitara AM6412

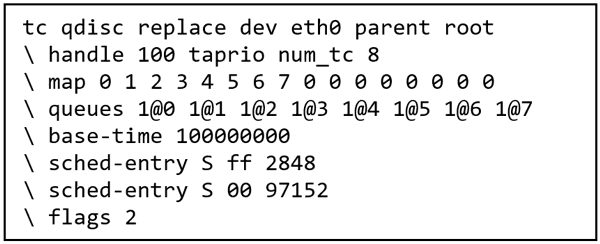

Wireshark Capture of EtherCAT Frames - 1 ms Cycle TimeThese jitter results are consistent with a typical RT Linux system interrupt latency [12]. Steps as shown in [13] [14] can be used to get this down to the low tens of microseconds. This is still at least two or even three orders of magnitude higher than what is achievable with TTS approaches. Instead of using TTS with EtherCAT, a schedule was created using the TSN feature of EST, where all the transmit gates are closed, but at every 100 μs, the gate is open to send one frame out as shown in the command line snippet in Figure 4-5.

Figure 4-5 Command for EST Schedule to

Achieve Time Triggered Send

Figure 4-5 Command for EST Schedule to

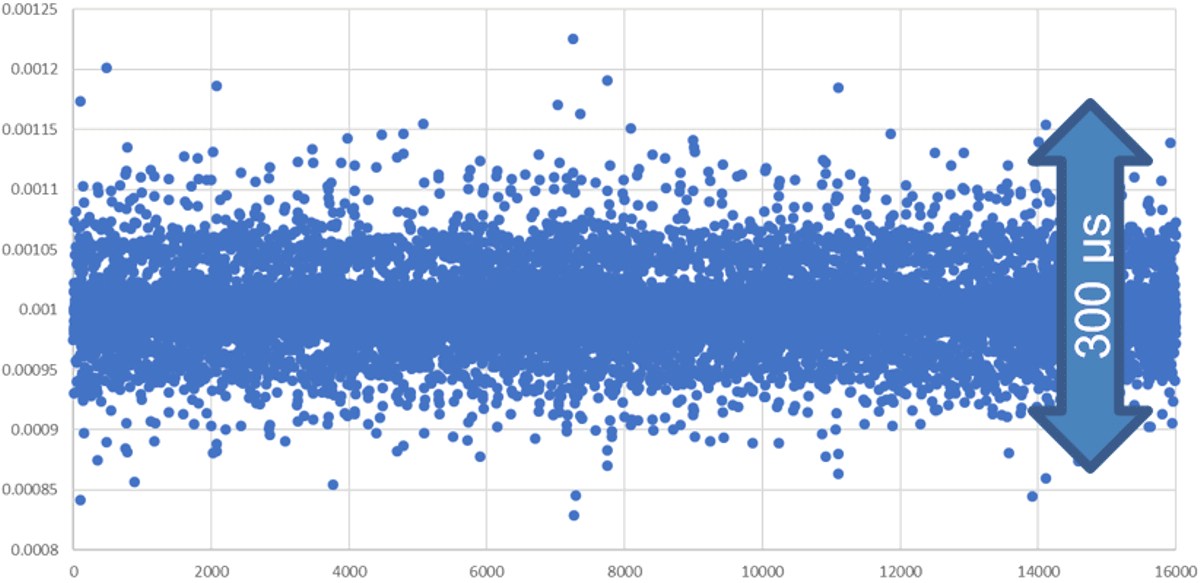

Achieve Time Triggered SendThe command in Figure 4-5 can initially look complex; however, details are explained in [15]. The two lines with "sched-entry" are important for achieving TTS. These lines specify that for 2848 nanoseconds, all 8 queues (ff, bitmap of 8 queues) are open, while for 97152 nanoseconds, all gates are closed (00). This schedule enables sending one frame at a time, assuming the application has completed its processing and has the frame ready to be sent. To simulate an EtherCAT Main sending to a Subordinate, an AM625 starter kit was used as an endpoint (in place of the Main) and a Sitara AM6412 configured as a bridge (in place of the Subordinate). Plget packet generator was used to generate traffic that represents the EtherCAT Main. Plget hardware timestamping of the receive Ethernet port was used by the Subordinate. The inter packet gap of a run of 10k packets with the EST schedule from Figure 4-5 was within -2 ns to +10 ns, as shown in Figure 4-6.

Figure 4-6 Inter Packet Gap in Microseconds

of 10k Frames at 1 Gbit/s with a 100 µs EST Shaper

Figure 4-6 Inter Packet Gap in Microseconds

of 10k Frames at 1 Gbit/s with a 100 µs EST ShaperFigure 4-7 shows a TX_EN RGMII measurement of the Codesys EtherCAT Main setup with the EST schedule. This figure is comparable to the baseline TX_EN RGMII measurement in Figure 4-2 without the EST schedule. The time duration due to the length on the wire of sending one frame at 100Mbits/s is ~110 μs.

Figure 4-7 TX_EN Timing of EST Shaped Codesys

EtherCAT Main - 1.5 ms Cycle Time, Oscilloscope in Persistence Mode

Figure 4-7 TX_EN Timing of EST Shaped Codesys

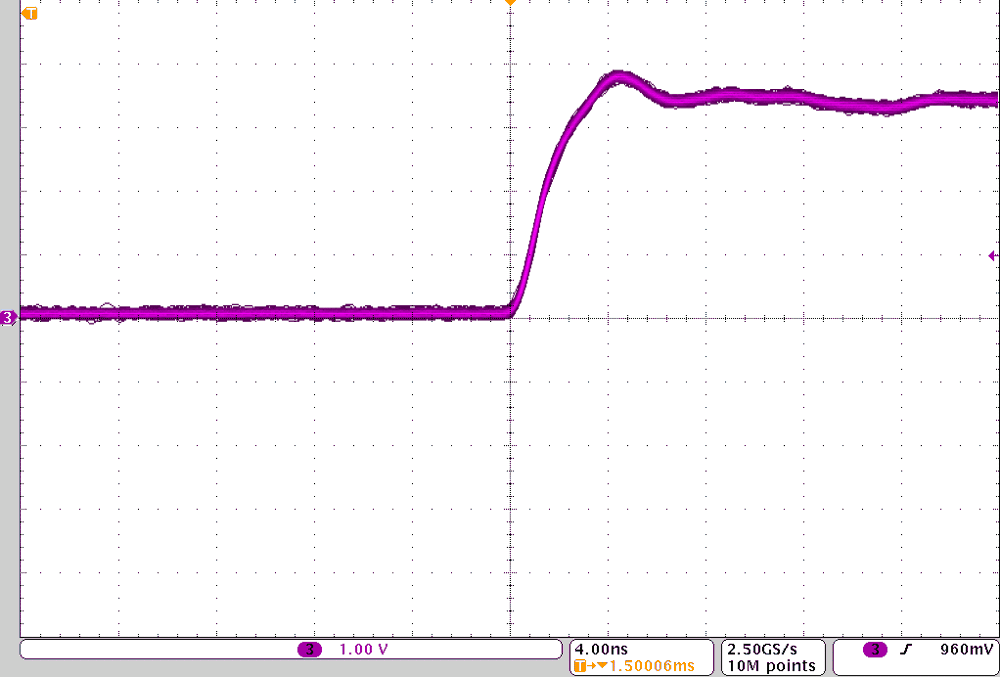

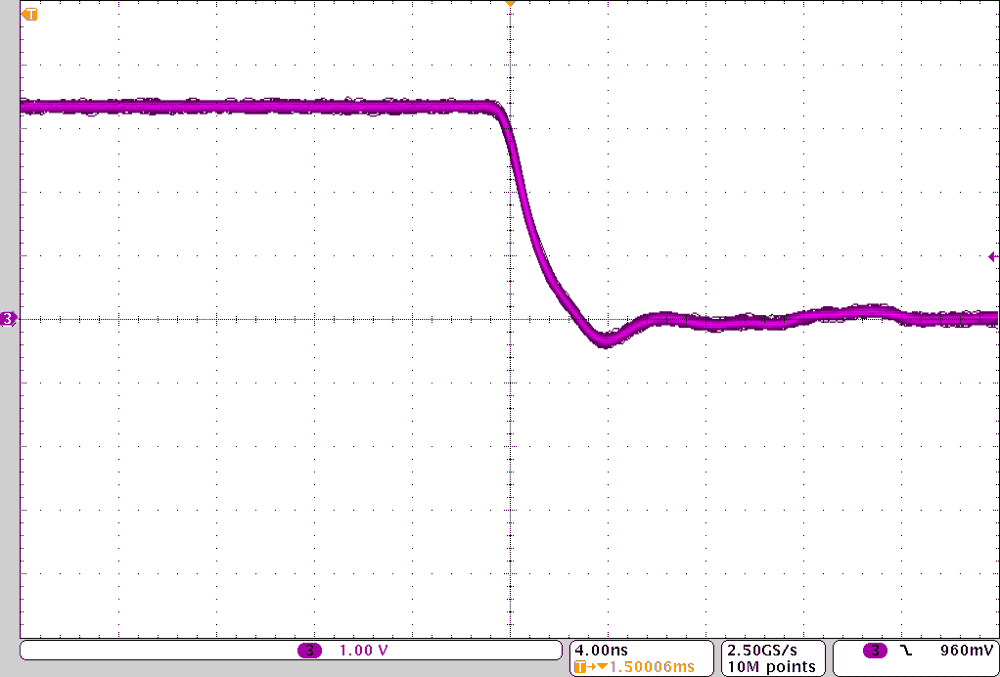

EtherCAT Main - 1.5 ms Cycle Time, Oscilloscope in Persistence ModeIn terms of jitter, the start of frame jitter at 10 ns is not visible at this resolution in the TX_EN signal. Figure 4-8 and Figure 4-9 shows a magnified view into the beginning and ending of sending the frame. This confirms jitter below 10 ns.

Figure 4-8 Magnified View of Beginning of

TX_EN Signal for EST Shaped Codesys EtherCAT Main - 1.5 ms Cycle Time, Oscilloscope

in Persistence Mode

Figure 4-8 Magnified View of Beginning of

TX_EN Signal for EST Shaped Codesys EtherCAT Main - 1.5 ms Cycle Time, Oscilloscope

in Persistence Mode Figure 4-9 Magnified View of Ending of TX_EN

Signal for EST Shaped Codesys EtherCAT Main - 1.5 ms Cycle Time, Oscilloscope in

Persistence Mode

Figure 4-9 Magnified View of Ending of TX_EN

Signal for EST Shaped Codesys EtherCAT Main - 1.5 ms Cycle Time, Oscilloscope in

Persistence Mode