-

TLV906xS コスト重視システム向け 10MHz、RRIO、CMOS オペアンプ

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- Device Comparison Table

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Information: TLV9061

- 5.5 Thermal Information: TLV9061S

- 5.6 Thermal Information: TLV9062

- 5.7 Thermal Information: TLV9062S

- 5.8 Thermal Information: TLV9064

- 5.9 Thermal Information: TLV9064S

- 5.10 Electrical Characteristics

- 5.11 Typical Characteristics

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

- 重要なお知らせ

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- DPW|5

発注情報

TLV906xS コスト重視システム向け 10MHz、RRIO、CMOS オペアンプ

このリソースの元の言語は英語です。 翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

1 特長

- レール ツー レール入出力

- 低い入力オフセット電圧:±0.3mV

- ユニティ ゲイン帯域幅:10MHz

- 低い広帯域ノイズ:10nV/√ Hz

- 低い入力バイアス電流:0.5pA

- 低い静止電流:538µA

- ユニティ ゲイン安定

- 内部 RFI および EMI フィルタ

- 最低 1.8V の電源電圧で動作

- 抵抗性の開ループ出力インピーダンスにより、大きな容量性負荷でも簡単に安定

- シャットダウン バージョン:TLV906xS

- 拡張温度範囲:-40℃~125℃

3 概要

TLV9061 (シングル)、TLV9062 (デュアル)、TLV9064 (クワッド) は、レール ツー レールの入力および出力スイング機能を備えたシングル / デュアル / クワッド低電圧 (1.8V~5.5V) オペアンプです。

これらのデバイスは、低電圧での動作、小さな占有面積、大きな容量性負荷の駆動が必要なアプリケーション向けの、コスト効率の優れた選択肢です。

TLV906x の容量性負荷駆動能力は 100pF ですが、開ループ出力インピーダンスは抵抗性なので、大きい容量性の負荷でも簡単に安定できます。これらのオペアンプは低電圧 (1.8V~5.5V) で動作し、OPAx316 および TLVx316 デバイスと同様の性能仕様を満たすよう、特別に設計されています。

TLV906xS デバイスにはシャットダウン モードが備わっており、標準消費電流 1µA 未満で、アンプをスタンバイ モードに切り替えることができます。

TLV906xSファミリはユニティ ゲイン安定で、RFIおよびEMI除去フィルタが内蔵され、オーバードライブ状況で位相反転が発生しないため、システムの設計を簡素化するため役立ちます。

すべてのチャネル バリエーション (シングル、デュアル、クワッド) で、X2SON、X2QFN などのマイクロサイズ パッケージと、SOIC、MSOP、SOT-23、TSSOP などの業界標準パッケージが利用可能です。

| 部品番号 (3) | パッケージ (1) | 本体サイズ (公称)(4) |

|---|---|---|

| TLV9061 | DBV (SOT-23、5) | 2.90mm × 1.60mm |

| DCK (SC70、5) | 2.00mm × 1.25mm | |

| DRL (SOT-553、5)(2) | 1.60mm × 1.20mm | |

| DPW (X2SON、5) | 0.80mm × 0.80mm | |

| TLV9061S | DBV (SOT-23、6) | 2.90mm × 1.60mm |

| DRY (USON、6) | 1.45mm × 1.00mm | |

| TLV9062 | D (SOIC、8) | 4.90mm × 3.90mm |

| PW (TSSOP、8) | 3.00mm × 4.40mm | |

| DGK (VSSOP、8) | 3.00mm × 3.00mm | |

| DDF (SOT-23、8) | 2.90mm × 1.60mm | |

| DSG (WSON、8) | 2.00mm × 2.00mm | |

| TLV9062S | DGS (VSSOP、10) | 3.00mm × 3.00mm |

| RUG (X2QFN、10) | 2.00mm × 1.50mm | |

| YCK (DSBGA、9) | 1.00 mm × 1.00mm | |

| TLV9064 | D (SOIC、14) | 8.65mm × 3.90mm |

| PW (TSSOP、14) | 5.00mm × 4.40mm | |

| RTE (WQFN、16) | 3.00mm × 3.00mm | |

| RUC (X2QFN、14) | 2.00mm × 2.00mm | |

| TLV9064S | RTE (WQFN、16) | 3.00mm × 3.00mm |

シングル ポールのローパス フィルタ

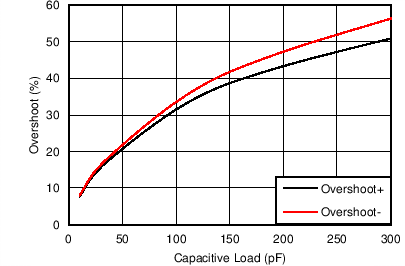

シングル ポールのローパス フィルタ 小信号のオーバーシュートと負荷容量との関係

小信号のオーバーシュートと負荷容量との関係