Sheng-Yang Yu

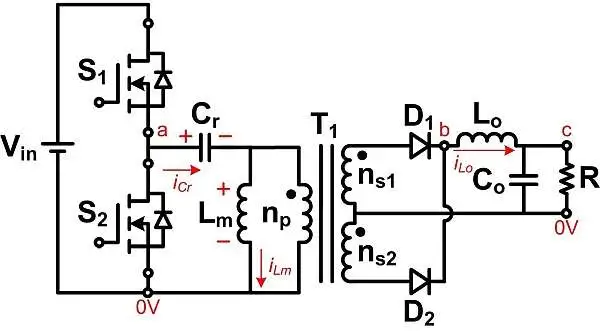

電源業界では 10 年以上にわたって、図 1 に示す、2 つの共振インダクタ (2 つの Ls:Lm と Lr)と 1 つの共振コンデンサ (1 つの C:Cr) を備えたインダクタ - インダクタ - コンデンサ (LLC) 直列共振コンバータ (LLC-SRC) が、低コストで高効率の絶縁型出力段として広く適用されています。LLC-SRC は、複雑な制御方式を必要としないソフト スイッチング特性を備えています。そのソフト スイッチング特性により、電圧定格の低い部品を使用することができ、コンバータ効率も高くなります。50% の固定デューティ サイクルで可変周波数変調を行うというシンプルな制御方式により、位相シフト フルブリッジ コンバータのような他のソフト スイッチング トポロジで使用されるコントローラと比較して、コントローラのコストを低く抑えることができます。

図 1 LLC-SRC

図 1 LLC-SRCLLC-SRC はハード スイッチングのフライバック コンバータやフォワード コンバータよりもはるかに高い効率を達成できますが、最高の効率を目指そうとすると、まだいくつかの設計上の課題があります。まず、LLC-SRC の設計では、十分に広い制御可能範囲を確保するために、2 つの共振インダクタの比率 (Lm 対 Lr) をおそらく 10 より小さくする必要があります。同時に、循環電流を小さくするために Lm に大きなインダクタンスが必要になります。これは、共振インダクタの比率を低く保つために Lr インダクタンスを大きく保つ必要があることを意味します。

直列共振インダクタ Lr の電流は、DC 成分を含まない完全な AC であり、これは磁束密度の変動が大きい (ΔB が大きい) ことを意味します。ΔB が大きいということは、AC 関連のインダクタ損失が大きいことを意味しています。インダクタがフェライト ベースのコアに巻かれている場合、コアのエアギャップ付近で生ずるフリンジング効果により巻線損失が大きくなります。

Lr のインダクタンスが大きいと、インダクタの巻数が増えて、AC 巻線損失が増えます。このため、多くの LLC-SRC 設計では、巻線損失とコア損失の間のトレードオフとして、共振インダクタに鉄粉ベースのコアを適用しています。それでも、ΔB が大きいと、共振インダクタでかなりの損失が発生し、巻線損失が大きくなるか、コア損失が大きくなります。

LLC-SRC 設計における 2 番目の課題は、同期整流器 (SR) 制御をいかに最適化するかということです。LLC-SRC 整流器の電流導通タイミングは、負荷条件とスイッチング周波数に依存します。LLC-SRC SR 制御で最も有望と考えられているのは、SR の電界効果トランジスタ (FET) のドレインとソース間電圧 (VDS) をセンシングし、VDS が特定のレベルを下回ったときまたは上回ったときに SR をオン / オフする方法です。VDS をセンシングする方式にはミリボルト レベルの精度が求められるため、IC でしか実現できません。LLC-SRC は電流供給型コンデンサ負荷の出力構成であるため、自己駆動型や他の低コストの SR 制御方式は適用できません。そのため、LLC-SRC SR コントローラ回路のコストは、他のトポロジよりも一般的に高くなります。

大きいインダクタ損失と SR 制御という 2 つの課題に対処しながら、共振コンバータが提供できる利点の大半を活用するには、図 2 に示す改良型 CLL マルチ共振コンバータ (CLL-MRC) の使用を検討してください。

図 2 改良型 CLL-MRC

図 2 改良型 CLL-MRC3 つの共振素子 (1 つのコンデンサと 2 つのインダクタ) がすべて入力側にある CLL-MRC とは異なり、図 2 に示すように、改良型 CLL-MRC では 1 つのインダクタを入力側から出力側に移動し、そのインダクタを整流器 – Lo の後に配置します。この変更により、共振インダクタに DC 電流を流すことができるため、ΔB が小さくなり、磁気損失も減少する可能性があります。

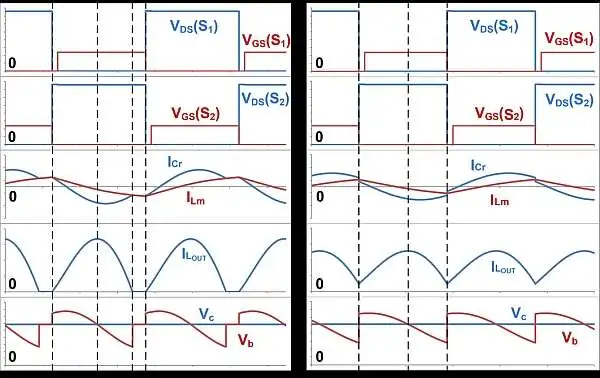

図 3 に改良型 CLL-MRC の動作を示します。fsw はコンバータのスイッチング周波数、fr1 = {2π[Cr (Lr1 //Lr2 )]0.5 } -1 は 2 つの共振周波数のうちの一方です。fsw が fr1 を下回ると、出力巻線電流は、LLC-SRC の出力巻線電流のように、スイッチング期間が終了する前にゼロに低下します。これで、出力にはインダクタが存在することになります。単純なコンデンサと抵抗のセットで、出力インダクタ電圧をセンシングできます。大きな電圧変化率 (dV/dt) が発生するたびに、SRS をオンまたはオフにするタイミングとなります。したがって、SR 制御方式は V DS センシング方式よりもコストがかかりません。

f sw が fr1 を上回ると、出力インダクタ電流は連続導通モードで動作します。つまり、ΔB が小さくなり、インダクタの AC 損失が非常に小さくなり、コンバータ効率が LLC-SRC よりも高くなる可能性があります。

図 3 改良型 CLL-MRC の主な波形:fsw < fr1 (左)、fsw > fr1 (右)

図 3 改良型 CLL-MRC の主な波形:fsw < fr1 (左)、fsw > fr1 (右)これらの性能の前提を検証するために、まったく同じ部品とパラメータを使用して、LLC-SRC と改良型 CLL-MRC の電力段を構築しました。唯一の違いは、72μH インダクタを LLC-SRC の共振インダクタに、1μH インダクタを改良型 CLL-MRC の出力インダクタに採用したことです。

図 4 に、両方の電力段の効率測定値を示します。入力電圧が低い場合、fsw は fr1 より小さいため、改良型 CLL-MRC の Lo 電流は ΔB が大きい不連続導通モードのままです。したがって、この動作条件では、改良型 CLL-MRC には効率に関する利点はありません。

入力電圧が高くなると、fsw は fr1 を上回り、Lo 電流は連続導通モードになります。430V 入力の場合、改良型 CLL-MRC の効率は LLC-SRC に比べて 1% 高くなります。この比較から、常に fr1 より高い周波数で動作するように改良型 CLL-MRC を設計すれば、その効率性能は範囲全体にわたって LLC-SRC より優れたものになることがわかります。

図 4 さまざまな入力電圧レベルにおけるコンバータ効率:改良型 CLL-MRC (上)、LLC-SRC (下)

図 4 さまざまな入力電圧レベルにおけるコンバータ効率:改良型 CLL-MRC (上)、LLC-SRC (下)LLC-SRC は実際に優れたトポロジであり、多くの魅力的な機能を持っています。ただし、アプリケーションによっては、最良のソリューションとは限りません。より低い回路コストでより優れた効率を達成するためには、場合によって既成概念にとらわれない発想が必要です。

参考情報

- テキサス・インスツルメンツのパワー サプライ デザイン セミナー関連資料:

- 『400VDC 入力~28V/9A 出力、小型高効率 CLL 共振コンバータのリファレンス デザイン』をご確認ください。

関連記事

- 『LLC 共振トポロジによりスイッチング損失を低減し、効率を高める』

- 『デジタル制御を使用した高効率共振モードの実装』

- 『ハーフブリッジ共振 LLC コンバータと 1 次側 MOSFET を選択する際の設計上の考慮事項』

- 『疑似共振コンバータと共振コンバータの使用』

- 『Power Tips #77:『CCM フライバック コンバータの設計』

この記事は、以前 EDN.com で公開された記事です。

重要なお知らせと免責事項

TI は、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションが適用される各種規格や、その他のあらゆる安全性、セキュリティ、またはその他の要件を満たしていることを確実にする責任を、お客様のみが単独で負うものとします。上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、TI の販売条件(www.tij.co.jp/ja-jp/legal/termsofsale.html)、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用されるTI の保証または他の保証の放棄の拡大や変更を意味するものではありません。IMPORTANT NOTICE

Copyright © 2024, Texas Instruments Incorporated

日本語版 日本テキサス・インスツルメンツ株式会社