SLAAE75A November 2022 – March 2023 MSPM0L1105 , MSPM0L1106 , MSPM0L1303 , MSPM0L1304 , MSPM0L1304-Q1 , MSPM0L1305 , MSPM0L1305-Q1 , MSPM0L1306 , MSPM0L1306-Q1 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346

8.5 Communicate With 1.8-V Devices Without a Level Shifter

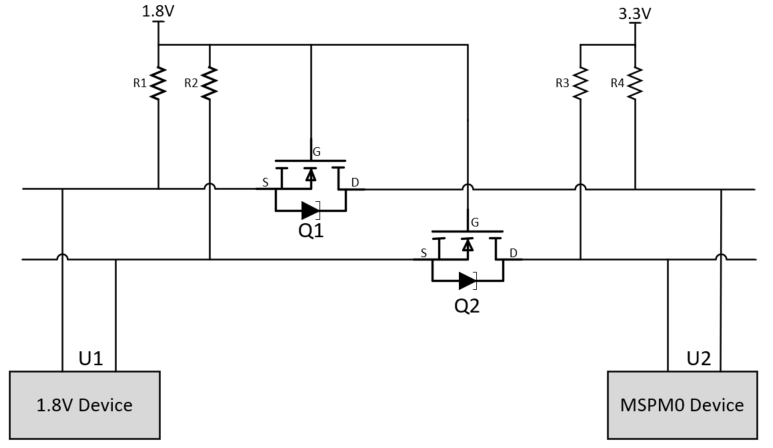

The MSPM0L series devices use a 3.3-V logic level (excluding ODIO). To communicate with 1.8-V devices without an external level shifter device, #GUID-5B093D09-9DC9-4408-9B12-7F6341B2D9EA shows a suggested circuit for interfacing with a 1.8-V device.

Figure 8-2 Suggested Communication Circuit With 1.8-V Device

Figure 8-2 Suggested Communication Circuit With 1.8-V DeviceTwo MOSFET are used in this circuit - check the VGS to ensure this MOSFET be able to fully turn on with a low RDS(on): for a 1.8-V device, use less than 1.8-V VGS MOSFET. However, do not use a too low VGS MOSFET, as this causes the MOSFET to turn on at a very small voltage (MCU logic judges it as 0), resulting in communication logic error.

U1 output and U2 input

- U1 output "1.8 V high", Q1 VGS around 0, thus Q1 turn off, U2 reads "3.3 V high" with R4.

- U1 output "low", Q1 VGS near 1.8 V, thus Q1 turn on, U2 reads "low".

U1 input and U2 output

- U2 output "3.3 V high", U1 keeps 1.8 V with R1, and Q1 turns off, thus U1 reads "1.8 V high".

- U2 output "low", U1 keeps 1.8 V with R1 at first, but the diode in the MOSFET pulls down U1 to 0.7 V (diode voltage drops), and then causes VGS to be greater than the turn-on voltage, Q1 turns on, and U1 reads "low".