SLAAE75A November 2022 – March 2023 MSPM0L1105 , MSPM0L1106 , MSPM0L1303 , MSPM0L1304 , MSPM0L1304-Q1 , MSPM0L1305 , MSPM0L1305-Q1 , MSPM0L1306 , MSPM0L1306-Q1 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346

5.1 Debug Port Pins and Pinout

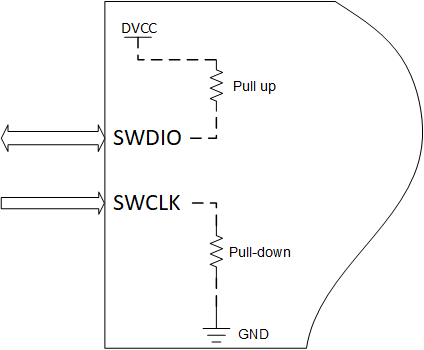

The debug port contains SWCLK and SWDIO (see Table 5-1) which have internal pull-down and pull-up resistors (see #GUID-32153E07-E091-4526-849C-85F1438E47D6). The MSPM0L MCU family is offered in various packages with different numbers of available pins. Refer to the device-specific data sheet for details.

Table 5-1 MSPM0L Debug Ports

| Device Signal | Direction | SWD Function |

|---|---|---|

| SWCLK | Input | Serial wire clock from debug probe |

| SWDIO | Input/Output | Bi-directional (shared) serial wire data |

Figure 5-2 MSPM0L SWD Internal Pull

Figure 5-2 MSPM0L SWD Internal Pull