SLAAE75A November 2022 – March 2023 MSPM0L1105 , MSPM0L1106 , MSPM0L1303 , MSPM0L1304 , MSPM0L1304-Q1 , MSPM0L1305 , MSPM0L1305-Q1 , MSPM0L1306 , MSPM0L1306-Q1 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346

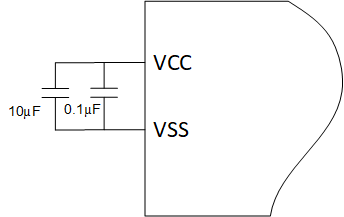

2.4 Recommended Decoupling Circuit for Power Supply

It is recommended to connect a combination of a 10-μF plus a 100-nF low-ESR ceramic decoupling capacitor to the DVCC pin (see #FIG_MYT_TMC_GVB). Higher-value capacitors can be used but can impact supply rail ramp-up time. Decoupling capacitors must be placed as close as possible to the pins that they decouple (within a few millimeters).

Figure 2-3 Power Supply Decoupling Circuit

Figure 2-3 Power Supply Decoupling Circuit