SLAAEI9 December 2023 MSPM0C1103 , MSPM0C1103-Q1 , MSPM0C1104 , MSPM0C1104-Q1 , MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G1519 , MSPM0G3105 , MSPM0G3105-Q1 , MSPM0G3106 , MSPM0G3106-Q1 , MSPM0G3107 , MSPM0G3107-Q1 , MSPM0G3505 , MSPM0G3505-Q1 , MSPM0G3506 , MSPM0G3506-Q1 , MSPM0G3507 , MSPM0G3507-Q1 , MSPM0G3519 , MSPM0L1105 , MSPM0L1106 , MSPM0L1117 , MSPM0L1227 , MSPM0L1227-Q1 , MSPM0L1228

- 1

- Abstract

- Trademarks

- 1MSPM0 Portfolio Overview

-

2Ecosystem And Migration

- 2.1 Ecosystem Comparison

- 2.2 Migration Process

- 2.3 Example

- 3Core Architecture Comparison

- 4Digital Peripheral Comparison

- 5Analog Peripheral Comparison

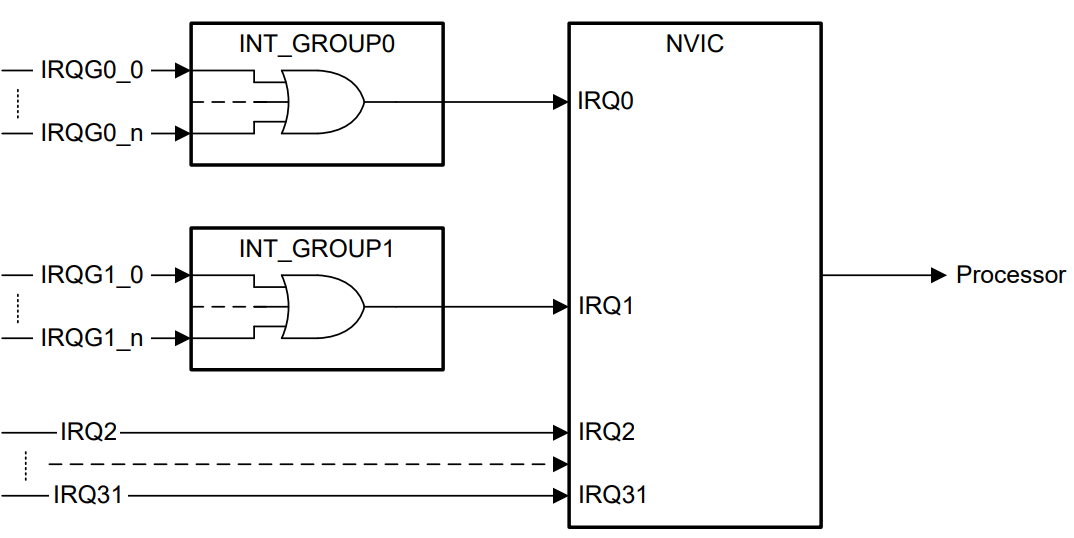

3.6.1.1 Interrupt Management of MSPM0

MSPM0 devices set the priority level of each peripheral interrupt source through the IPRx registers in the NVIC, and mask/unmask a peripheral interrupt source through ISER and ICER register in the NVIC. Each peripheral interrupt contains kinds of interrupt conditions. For example, as a peripheral interrupt source, UARTx has multiple interrupt conditions such as transmit interrupt and receive interrupt, and so forth. And the interrupt conditions are managed by six standard registers in the peripheral side. Figure 3-2 shows the peripheral interrupt hierarchy.

Figure 3-2 Peripheral Interrupt Hierarchy

of MSPM0

Figure 3-2 Peripheral Interrupt Hierarchy

of MSPM0