SLVUBT8B November 2020 – June 2022 LP8764-Q1 , TPS6594-Q1

- Scalable PMIC's GUI User’s Guide

- Trademarks

- 1 Introduction

- 2 Supported Features

- 3 Revisions

- 4 Overview

- 5 Getting Started

- 6 Quick-start Page

- 7 Register Map Page

- 8 NVM Configuration Page

- 9 NVM Validation Page

- 10Watchdog Page

- 11Additional Resources

- 12Appendix A: Troubleshooting

- 13Appendix B: Advanced Topics

- 14Appendix C: Known Limitations

- 15Appendix D: Migration Topics

- 16Revision History

5.4 Connecting to a PMIC

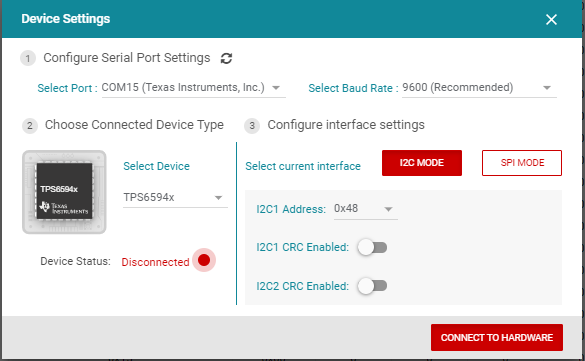

The GUI and AEVM support both I2C and SPI with and without CRC. As mentioned previously, when entering the Register Map and Quick-start pages, the GUI will attempt to connect to any device with a non-CRC I2C interface at address 0x48. If an alternate address or configuration is needed, then the Device Settings window is provided to change the settings, as shown in Figure 5-7. This window can also be accessed in the drop-down menu below Options.

Figure 5-7 Device Settings From Options

Tab

Figure 5-7 Device Settings From Options

Tab Figure 5-8 Device Interface

Settings

Figure 5-8 Device Interface

SettingsAs shown in Figure 5-8, options are provided to select the device as well as the interface.

Select Device

The device selection will determine the register interpretation of data written to and read from the PMIC. Failure to select the correct device can result in erroneous data being written to the PMIC or data read from the PMIC to be misinterpreted.

I2C

The I2C1 address selection is limited to valid page 0 addresses of the PMIC. Once the I2C1 address is specified, the GUI will automatically determine the addresses for pages 1-4 as well as determine if the physical I2C2 interface for page 4 is to be used.

SPI

Similar to the I2C implementation, the GUI will automatically update the page information during communication.

The latest AEVM controller firmware will support multi-PMIC operation by providing individual chip select (CS) control. As shown in Figure 5-9, up to 6 PMICs can be cascaded in a primary/secondary configuration and communication with each device is controlled by the chip selection. Table 5-1 shows the relationship with the AEVM GPIO.

| Chip Select | AEVM Port |

|---|---|

| Multi-PMIC is not selected | PD2, QSSI module CS is used |

| 1 | PD2, QSSI module CS is used |

| 2 | PD7 |

| 3 | PC7 |

| 4 | PC6 |

| 5 | PC5 |

| 6 | PC4 |

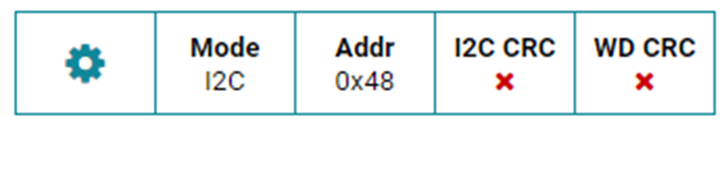

Updating the Interface

In addition to the Option tab at the top of the GUI, in the Quick-start, Register Map, and Watchdog pages, there is a device settings bar that shows the current interface selection. Clicking the gear icon within the bar also opens the Device Settings window. In the NVM Configuration and NVM Validation pages, the interface selection is provided within the page. Please refer to those sections for more details.

Figure 5-10 Device Settings Bar

Figure 5-10 Device Settings BarConnecting to a device is not required to access the GUI pages. Specifically, connecting to a device is not required to create an NVM configuration as described in section Section 8