SPRACT6A october 2020 – march 2023 F29H850TU , F29H850TU , F29H859TU-Q1 , F29H859TU-Q1 , TMS320F2800132 , TMS320F2800132 , TMS320F2800133 , TMS320F2800133 , TMS320F2800135 , TMS320F2800135 , TMS320F2800137 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280023C , TMS320F280025 , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280033 , TMS320F280034 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C , TMS320F280049C-Q1 , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28076 , TMS320F28374D , TMS320F28374D , TMS320F28374S , TMS320F28374S , TMS320F28375D , TMS320F28375D , TMS320F28375S , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376D , TMS320F28376S , TMS320F28376S , TMS320F28377D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378D , TMS320F28378S , TMS320F28378S , TMS320F28379D , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28379S , TMS320F28384D , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388D , TMS320F28388S , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1 , TMS320F28P659SH-Q1

- Abstract

- Trademarks

- 1Introduction

- 2Input Settling Design Steps

-

3Example Circuit Design

- 3.1 Select the ADC

- 3.2 Find the Minimum Op-Amp Bandwidth and RC Filter Ranges

- 3.3 Verify the Op-amp Model

- 3.4 Build the ADC Input Model

- 3.5 DC Node Analysis

- 3.6 Refine RC Filter Values Via Simulation (Part 1)

- 3.7 Refine RC Filter Values Via Simulation (Part 2)

- 3.8 Refine RC Filter Values Via Simulation (Part 3)

- 3.9 Further Refinement

- 3.10 Further Simulations

- 3.11 Completed Worksheet

- 4Working With Existing Circuits or Additional Constraints

- 5Summary

- 6References

- 7Revision History

3.6 Refine RC Filter Values Via Simulation (Part 1)

Now that the circuit is setup for simulation, the first step is to run a basic transient analysis to ensure everything is functioning and to check the initial settling. The transient analysis can be run via the TINA-TI menu options: Analysis → Transient...

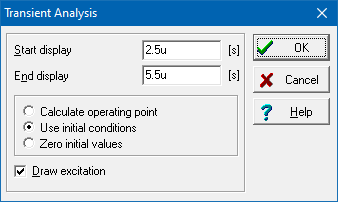

The settling should be captured after allowing the circuit to stabilize for a couple sampling cycles, so a time period of 2.5 μs to 5.5 μs is selected as shown in Figure 3-5. This allows capture of the full 3rd and 4th sampling cycles (each cycle is 1us since the trigger frequency is 1 MHz).

Figure 3-5 F280049 Example Transient

Analysis Configuration

Figure 3-5 F280049 Example Transient

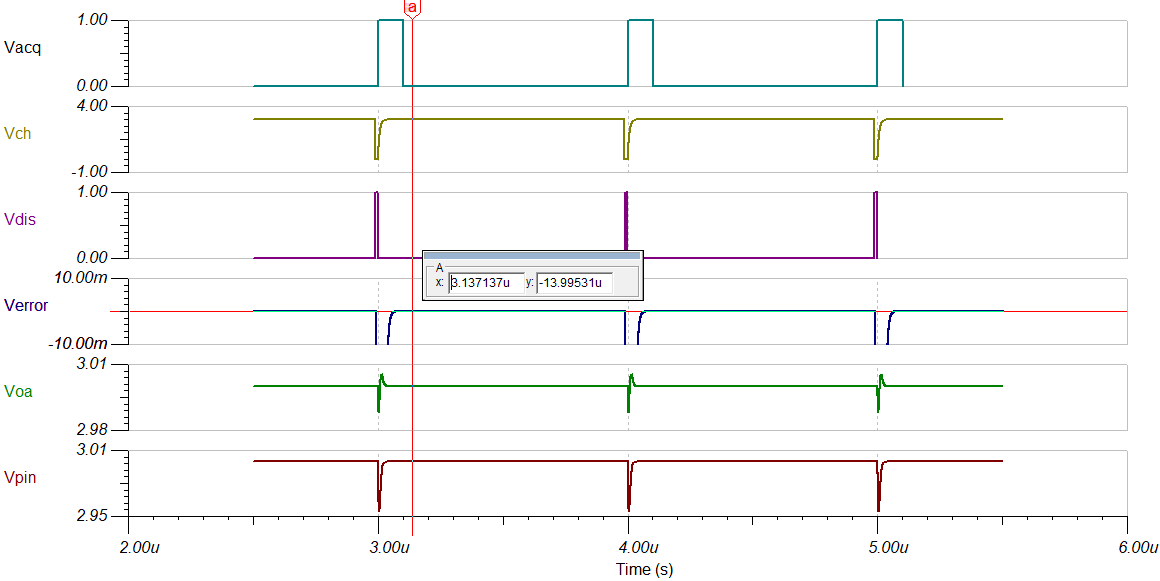

Analysis ConfigurationFigure 3-6 shows the output waveforms from the transient simulation after separating the outputs (View → Separate outputs). The error voltage scale has also been adjusted to show a range of +10 mV to -10 mV (double-click on Verror, then enter -10m in the "Lower limit" field and 10m in the "Upper limit" field, then click "OK").

From this output, it is clear that:

- Discharge and acquisition times are functioning as expected

- The transients on Voa and Vpin are of reasonable magnitude (less than 100 mV, so the signal settling will be considered a small signal event)

- Verror is settling to about 14 µV, which is well within the error target of 366 µV

Figure 3-6 F280049 Example Initial

Transient Results

Figure 3-6 F280049 Example Initial

Transient Results