-

TPS65132 Single Inductor - Dual Output Power Supply

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1

Low-current Applications (≤ 40 mA)

- 9.2.1.1 Design Requirements

- 9.2.1.2 Detailed Design Procedure

- 9.2.1.3 Application Curves

- 9.2.2

Mid-current Applications (≤ 80 mA)

- 9.2.2.1 Design Requirements

- 9.2.2.2 Detailed Design Procedure

- 9.2.2.3 Application Curves

- 9.2.3 High-current Applications (≤ 150 mA)

- 9.2.1

Low-current Applications (≤ 40 mA)

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

- IMPORTANT NOTICE

TPS65132 Single Inductor - Dual Output Power Supply

1 Features

- Input Voltage Range: 2.5 V to 5.5 V

- VPOS Boost Converter:

4 V to 6 V (0.1-V step) - VNEG Inverting Buck-Boost Converter:

–6 V to –4 V (0.1-V step) - Maximum Output Current:

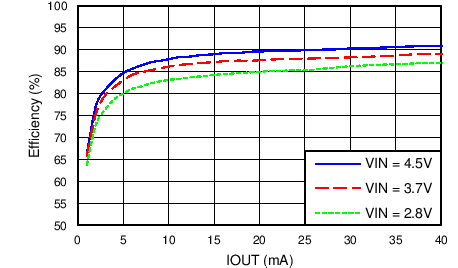

80 mA or 150 mA - Outstanding Combined Efficiency

- > 85% at IOUT > 10 mA

- > 90% at IOUT > 40 mA

- Excellent Performance

- Outstanding Transient Response

- 1% Output Voltage Accuracy over

Full Temperature Range

- I2C Interface

- Programmable Power-Up / -Down

Sequencing Options - Flexible Output Voltage Programming

- Programmable Active Output Discharge

- > 1000x Programmable Non-Volatile Memory

- Programmable Power-Up / -Down

- Under-Voltage Lock-Out and Thermal Protection

- Two Package Options

- 15-Ball CSP Package

- 20-Pins QFN Package

2 Applications

- Small-, Medium-Size Bipolar LCD Displays

- Smartphone, Tablet

- Camera, GPS

- Home Automation, Point-of-Sales

- Wearables (Smart Watch, Activity Tracker)

- General Split-Rail Power Supply

- Differential Audio, Headphone Amplifier

- Instrumentation, Operational Amplifier, Comparator

- DAC / ADC

3 Description

The TPS65132 family is designed to supply positive/negative driven applications. The device uses a single inductor scheme for both outputs to provide the user smallest solution size, a small bill-of-material as well as high efficiency. The devices offer best line and load regulation at low noise. With its input voltage range of 2.5 V to 5.5 V, it is optimized for products powered by single-cell batteries (Li-Ion, Ni-Li, Li-Polymer) and fixed 3.3-V and 5-V rails. The TPS656132 family provides 80 mA and 150 mA output current options with programmability to 40 mA. There are both CSP and QFN package options available.

Device Information (1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM.) |

|---|---|---|

| TPS65132 -B, -L, -T, -S |

DSBGA (15) | 2.11 mm × 1.51 mm |

| TPS65132W | WQFN (20) | 4.00 mm × 3.00 mm |

- For all available packages, see the orderable addendum at the end of the datasheet.

space

space

Typical Application

Efficiency vs Output Current

4 Revision History

Changes from G Revision (August 2015) to H Revision

- Removed Product Preview from TPS65132S.Go

- Changed Device Comparison Table Go

- Added description of clock stretching Go

- Deleted detailed I2C interface description Go

- Added that the DLYx Register is only valid for TPS65132Sx versions. Go

- Changed Table 6 Go

Changes from F Revision (June 2015) to G Revision

- Changed scope figures for Boost Converter switching. Go

Changes from E Revision (November 2014) to F Revision

- Added TPS65132L1 device to Device Comparison table Go

- Added TPS65132T6 device to the Device Comparison Table. Go

- Separated LOGIC SCL, SDA spec MIN/MAX from LOGIC EN, ENN, ENP, SYNC spec MIN/MAXGo

- Changed DAC Registers section for clarity Go

- Added High-current Applications (≤ 150 mA) sectionGo

Changes from D Revision (October 2014) to E Revision

- Added TPS65132L0 device to Device Comparison table Go

Changes from C Revision (July 2014) to D Revision

- Changed package type to industry standard identifier in the Device Information table Go

Changes from B Revision (May 2014) to C Revision

- Added note to Device Comparison Table Go

- Added reference to Power-Down And Discharge (LDO) and Power-Down And Discharge (CPN) Go

- Added Table 1 and various references to itGo

- Added "Power-Down And Discharge (CPN) shows the VNEG discharge behavior of each device variant".Go

- Added Table 2 and various references to it Go

- Added note to Figure 18 Go

Changes from A Revision (August 2013) to B Revision

- Formatted to the new data sheet standard Go

- Added new package option (QFN) to Device Information table Go

- Added new package option (QFN) to Pin Configurations section Go

- Added the ESD Ratings table Go

Changes from * Revision (June 2013) to A Revision

- Added TPS65132Bx devices to the Device Comparison tableGo

5 Device Comparison Table

| PART NUMBER(1) | PRE-PROGRAMMED OUTPUT VOLTAGES |

IOUT_MAX | PRE-PROGRAMMED IOUT |

PRE-PROGRAMMED ACTIVE DISCHARGE(2) |

STARTUP TIME VPOS / VNEG (4) |

ISD | PACKAGE |

|---|---|---|---|---|---|---|---|

| TPS65132A | VPOS = 5.4 V VNEG = –5.4 V |

80 mA | 40 mA | VPOS / VNEG | FAST | 30 µA | CSP |

| TPS65132A0 | VPOS = 5.0 V VNEG = –5.0 V |

||||||

| TPS65132B | VPOS = 5.4 V VNEG = –5.4V |

80 mA | 40 mA | VPOS / VNEG | FAST | 130 nA | CSP |

| TPS65132B0 | VPOS = 5.0 V VNEG = –5.0 V |

||||||

| TPS65132B5 | VPOS = 5.5 V VNEG = –5.5 V |

||||||

| TPS65132B2 | VPOS = 5.2 V VNEG = –5.2 V |

80 mA | 40 mA | VPOS / VNEG | SLOW | 130 nA | CSP |

| TPS65132L | VPOS = 5.4 V VNEG = –5.4 V |

||||||

| TPS65132L0 | VPOS = 5.0 V VNEG = –5.0 V |

||||||

| TPS65132L1 (3) | VPOS = 5.1 V VNEG = –5.1 V |

80 mA | 40 mA | VPOS / VNEG | SLOW | 130 nA | CSP |

| TPS65132T6 | VPOS = 5.6 V VNEG = –5.6 V |

80 mA | 80 mA | VPOS / VNEG | SLOW | 130 nA | CSP |

| TPS65132S | VPOS = 5.4 V VNEG = –5.4 V |

150 mA | 80 mA | VPOS / VNEG | SLOW | 130 nA | CSP |

| TPS65132W | VPOS = 5.4 V VNEG = –5.4 V |

80 mA | 80 mA | VPOS / VNEG | SLOW | 130 nA | QFN |

6 Pin Configuration and Functions

Pin Functions

| PIN | I/O | DESCRIPTION | ||

|---|---|---|---|---|

| NAME | Ax, Bx, Lx, Tx | Sx | ||

| AGND | D2 | D2 | — | Analog ground |

| CFLY1 | C3 | C3 | I/O | Negative charge pump flying capacitor pin |

| CFLY2 | A3 | A3 | I/O | Negative charge pump flying capacitor pin |

| EN | — | B1 | Enable pin (sequence programmed) | |

| ENN | A1 | — | I | Enable pin for VNEG rail |

| ENP | B1 | B1 | I | Enable pin for VPOS rail |

| OUTP | E3 | E3 | O | Output pin of the LDO (VPOS) |

| OUTN | A2 | A2 | O | Output pin of the negative charge pump (VNEG) |

| PGND | B3 | B3 | — | Power ground |

| E1 | E1 | |||

| REG | D3 | D3 | I/O | Boost converter output pin |

| E2 | E2 | |||

| SCL | B2 | B2 | I/O | I²C interface clock signal pin |

| SDA | C2 | C2 | I/O | I²C interface data signal pin |

| SW | D1 | D1 | I/O | Switch pin of the boost converter |

| SYNC | — | A1 | I | Synchronization pin. 150 mA current enabled if this pin is pulled HIGH. |

| VIN | C1 | C1 | I | Input voltage supply pin |

Pin Functions

| PIN | I/O | DESCRIPTION | |

|---|---|---|---|

| NAME | Wx | ||

| AGND | 3 | — | Analog ground |

| 17 | |||

| CFLY1 | 13 | I/O | Negative charge pump flying capacitor pin |

| CFLY2 | 10 | I/O | Negative charge pump flying capacitor pin |

| ENN | 6 | I | Enable pin for VNEG rail |

| ENP | 5 | I | Enable pin for VPOS rail |

| OUTP | 16 | O | Output pin of the LDO (VPOS) |

| 15 | |||

| OUTN | 9 | O | Output pin of the negative charge pump (VNEG) |

| PGND | 1 | — | Power ground |

| 2 | |||

| 11 | |||

| 12 | |||

| REG | 14 | I/O | Boost converter output pin |

| 18 | |||

| SCL | 8 | I/O | I²C interface clock signal pin |

| SDA | 7 | I/O | I²C interface data signal pin |

| SW | 19 | I/O | Switch pin of the boost converter |

| 20 | |||

| VIN | 4 | I | Input voltage supply pin |