Packaging information

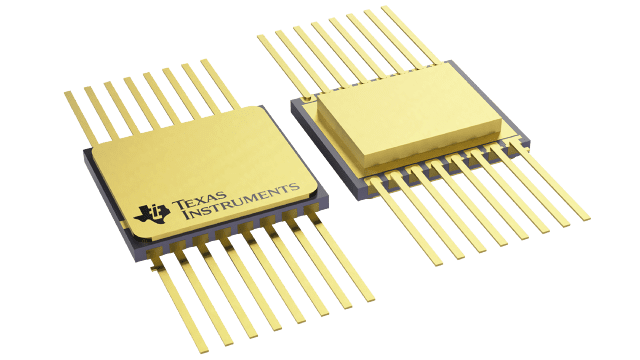

| Package | Pins CFP (HKR) | 16 |

| Operating temperature range (°C) 25 to 25 |

| Package qty | Carrier 25 | TUBE |

Features for the TPS7H1101A-SP

-

5962R13202

(1):

- Radiation hardness assurance (RHA) qualified up to total ionizing dose (TID) 100 krad(Si)

- ELDRS-free: 100 krad(Si)

- Dose rate: 10 mrad(Si)/s

- Single event latch-up (SEL) immune to LET = 85 MeV-cm2/mg

- SEB and SEGR immune to LET = 85 MeV-cm2/mg

- SET/SEFI onset threshold > 40

MeV-cm2/mg(2)

- Specifically designed to always upset low to avoid damage to critical downstream component

- SET/SEFI cross-section plot(2)

- Ultra-low VIN range: 1.5 V to 7 V

- 3-A maximum output current

- Current share/parallel operation to provide up to 6-A output current

- Stable with ceramic output capacitor

- ±2% accuracy over line, load, and temperature

- Programmable soft start through external capacitor

- Input enable across all input voltages and power-good output for power sequencing

- Ultra-low dropout LDO voltage: 62 mV at 1 A (25°C), VOUT = 1.8 V

- Low noise: 20.33 µVRMS, VIN = 2 V, VOUT = 1.8 V at 3 A

- PSRR: over 45 dB at 1 kHz

- Excellent load/line transient response

- Foldback current limit

- See the Design and development tab

- Thermally-enhanced CFP package, 0.4° C/W RθJC

Description for the TPS7H1101A-SP

The TPS7H1101A-SP is an improved version of the TPS7H1101-SP allowing the use of the enable feature across the entire input voltage range. It is a radiation-hardened LDO linear regulator that uses a PMOS pass element configuration. It operates over a wide range of input voltage, from 1.5 V to 7 V while offering excellent PSRR. The TPS7H1101A-SP features a precise and programmable foldback current limit implementation with a very-wide adjustment range. To support the complex power requirements of FPGAs, DSPs, or microcontrollers, the TPS7H1101A-SP provides enable on and off functionality, programmable soft start, current sharing capability, and a Power Good open-drain output.