JAJSMH6F July 2021 – August 2024 TPS7H5001-SP , TPS7H5002-SP , TPS7H5003-SP , TPS7H5004-SP

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Device Comparison Table

- 5 Device Options

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 Electrical Characteristics: All Devices

- 7.6 Electrical Characteristics: TPS7H5001-SP

- 7.7 Electrical Characteristics: TPS7H5002-SP

- 7.8 Electrical Characteristics: TPS7H5003-SP

- 7.9 Electrical Characteristics: TPS7H5004-SP

- 7.10 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 VIN and VLDO

- 8.3.2 Start-Up

- 8.3.3 Enable and Undervoltage Lockout (UVLO)

- 8.3.4 Voltage Reference

- 8.3.5 Error Amplifier

- 8.3.6 Output Voltage Programming

- 8.3.7 Soft Start (SS)

- 8.3.8 Switching Frequency and External Synchronization

- 8.3.9 Primary Switching Outputs (OUTA/OUTB)

- 8.3.10 Synchronous Rectifier Outputs (SRA and SRB)

- 8.3.11 Dead Time and Leading Edge Blank Time Programmability (PS, SP, and LEB)

- 8.3.12 Pulse Skipping

- 8.3.13 Duty Cycle Programmability

- 8.3.14 Current Sense and PWM Generation (CS_ILIM)

- 8.3.15 Hiccup Mode Operation (HICC)

- 8.3.16 External Fault Protection (FAULT)

- 8.3.17 Slope Compensation (RSC)

- 8.3.18 Frequency Compensation

- 8.3.19 Thermal Shutdown

- 8.4 Device Functional Modes

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Application

- 9.2.1 Design Requirements

- 9.2.2

Detailed Design Procedure

- 9.2.2.1 Switching Frequency

- 9.2.2.2 Output Voltage Programming Resistors

- 9.2.2.3 Dead Time

- 9.2.2.4 Leading Edge Blank Time

- 9.2.2.5 Soft-Start Capacitor

- 9.2.2.6 Transformer

- 9.2.2.7 Main Switching FETs

- 9.2.2.8 Synchronous Rectificier FETs

- 9.2.2.9 RCD Clamp

- 9.2.2.10 Output Inductor

- 9.2.2.11 Output Capacitance and Filter

- 9.2.2.12 Sense Resistor

- 9.2.2.13 Hiccup Capacitor

- 9.2.2.14 Frequency Compensation Components

- 9.2.2.15 Slope Compensation Resistor

- 9.2.3 Application Curves

- 9.3 Power Supply Recommendations

- 9.4 Layout

- 10Device and Documentation Support

- 11Revision History

- 12Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- HFT|22

- KGD|0

- PW|24

サーマルパッド・メカニカル・データ

発注情報

6 Pin Configuration and Functions

Figure 6-1 TPS7H5001-SP HFT Package

22-Pin CFP With Thermal Pad

(Top View)

22-Pin CFP With Thermal Pad

(Top View)

Figure 6-3 TPS7H5003-SP HFT Package

22-Pin CFP With Thermal Pad

(Top View)

22-Pin CFP With Thermal Pad

(Top View)

Figure 6-5 TPS7H5001-SP PW Package

24-Pin TSSOP

(Top View)

24-Pin TSSOP

(Top View)

Figure 6-7 TPS7H5003-SP PW Package

24-Pin TSSOP

(Top View)

24-Pin TSSOP

(Top View)

Figure 6-2 TPS7H5002-SP HFT Package

22-Pin CFP With Thermal Pad

(Top View)

22-Pin CFP With Thermal Pad

(Top View)

Figure 6-4 TPS7H5004-SP HFT Package

22-Pin CFP With Thermal Pad

(Top View)

22-Pin CFP With Thermal Pad

(Top View)

Figure 6-6 TPS7H5002-SP PW Package

24-Pin TSSOP

(Top View)

24-Pin TSSOP

(Top View)

Figure 6-8 TPS7H5004-SP PW Package

24-Pin TSSOP

(Top View)

24-Pin TSSOP

(Top View)

Table 6-1 Pin Functions

| PIN | I/O | DESCRIPTION | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| NAME | TPS7H5001-SP | TPS7H5002-SP | TPS7H5003-SP | TPS7H5004-SP | ||||||

| CFP | TSSOP | CFP | TSSOP | CFP | TSSOP | CFP | TSSOP | |||

| RT | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | I/O | In internal oscillation mode, the RT pin must be populated with a resistor to AVSS. When the RT pin is floating, a 200-kHz to 4-MHz external clock is required at the SYNC pin. The frequency of the external clock must be twice the desired switching frequency. |

| PS | 2 | 2 | 2 | 2 | — | — | — | — | I/O | Primary off to synchronous rectifier on dead-time set. Programmable through an external resistor to AVSS. |

| SP | 3 | 3 | 3 | 3 | — | — | — | — | I/O | Synchronous rectifier off to primary on dead-time set. Programmable through an external resistor to AVSS. |

| LEB | 4 | 4 | 4 | 4 | — | — | 4 | 4 | I/O | Leading edge blank time set. Programmable through an external resistor to AVSS. |

| HICC | 5 | 5 | 5 | 5 | 5 | 5 | 5 | 5 | I/O | Cycle-by-cycle current limit time delay and hiccup time setting. Delay time and hiccup time determined by capacitor from HICC to AVSS. Connecting this pin to AVSS disables hiccup mode. |

| SYNC | 6 | 6 | 6 | 6 | 6 | 6 | 6 | 6 | I/O | When the RT pin is floating, SYNC is configured as an input for a 200-kHz to 4-MHz external clock. In this case, the external clock input gets inverted and the system clock will run at half the frequency of the external clock input. When the RT pin is populated with a resistor to AVSS, SYNC outputs a 200-kHz to 4-MHz clock signal at twice the device switching frequency in phase with the switching of the device. |

| DCL | 7 | 7 | 7 | 7 | 7 | 7 | 7 | 7 | I/O | Duty cycle limit configurability. For TPS7H5001-SP, connect to AVSS for 50% duty cycle limit, floating for 75%, and VLDO for 100%. For TPS7H5002-SP and TPS7H5003-SP, the DCL pin can be left floating or connected to VLDO to set the maximum duty cycle to 75% or 100%, respectively. For TPS7H5004-SP, this pin must be connected to AVSS in order to obtain the 50% maximum duty cycle. |

| EN | 8 | 8 | 8 | 8 | 8 | 8 | 8 | 8 | I | Connecting the EN pin to the VLDO pin or external source greater than 0.6 V enables the device. In addition, input undervoltage lockout (UVLO) can be adjusted with two resistors. |

| VIN | 9 | 9 | 9 | 9 | 9 | 9 | 9 | 9 | I | Input supply to the device. Input voltage range is from 4 V to 14 V. |

| OUTA | 10 | 10 | 10 | 10 | 10 | 10 | 10 | 10 | O | Primary switching output A. |

| OUTB | 11 | 11 | — | — | — | — | 11 | 11 | O | Primary switching output B. Active only when DCL = AVSS. |

| SRB | 12 | 14 | — | — | — | — | — | — | O | Synchronous rectifier output B. Active only when DCL = AVSS. |

| SRA | 13 | 15 | 13 | 15 | 13 | 15 | — | — | O | Synchronous rectifier output A. |

| AVSS | 14 | 16 | 14 | 16 | 14 | 16 | 14 | 16 | — | Ground of the device. The thermal pad, lid, and seal ring of the device are internally connected to ground for the ceramic package (CFP). |

| VLDO | 15 | 17 | 15 | 17 | 15 | 17 | 15 | 17 | O | Output of internal regulator. Requires at least 1-μF external capacitor to AVSS. |

| CS_ILIM | 16 | 18 | 16 | 18 | 16 | 18 | 16 | 18 | I/O | Current sense for PWM control and cycle-by-cycle overcurrent protection. An input voltage over 1.05 V on CS_ILIM will trigger an overcurrent in the PWM controller. The sensed waveform on CS_ILIM contains a 150-mV offset when compared to the COMP/2 voltage at the input of the PWM comparator. |

| FAULT | 17 | 19 | 17 | 19 | 17 | 19 | 17 | 19 | I | Fault protection pin. When the rising threshold of the FAULT pin is exceeded, the outputs will stop switching. After the external voltage drops below the falling threshold, the device will restart after a set delay. Connect this pin to AVSS to disable FAULT. |

| REFCAP | 18 | 20 | 18 | 20 | 18 | 20 | 18 | 20 | O | 1.2-V internal reference. Requires a 470-nF external capacitor to AVSS. |

| RSC | 19 | 21 | 19 | 21 | 19 | 21 | 19 | 21 | I/O | A resistor from RSC to AVSS sets the desired slope compensation. |

| SS | 20 | 22 | 20 | 22 | 20 | 22 | 20 | 22 | I/O | Soft start. An external capacitor connected to this pin sets the internal voltage reference rise time. The voltage on this pin overrides the internal reference. It can be used for tracking and sequencing. |

| VSENSE | 21 | 23 | 21 | 23 | 21 | 23 | 21 | 23 | I | Inverting input of the error amplifier. |

| COMP | 22 | 24 | 22 | 24 | 22 | 24 | 22 | 24 | I/O | Error amplifier output. Connect frequency compensation to this pin. |

| NC | N/A | 12, 13 | 11, 12 | 11, 12, 13, 14 | 2, 3, 4, 11, 12 | 2, 3, 4, 11, 12, 13, 14 | 2, 3, 12, 13 | 2, 3,12, 13, 14, 15 | — | No connect. Can be connected to AVSS to avoid floating metal if desired. |

Table 6-2 TPS7H500x-SP Bare Die Information -

Applicable for All Devices

| DIE THICKNESS | BACKSIDE FINISH | BACKSIDE POTENTIAL | BOND PAD METALLIZATION COMPOSITION | BOND PAD THICKNESS |

|---|---|---|---|---|

| 15 mils | Silicon with backgrind | GND | Al (0.5% Cu) | 3000 nm |

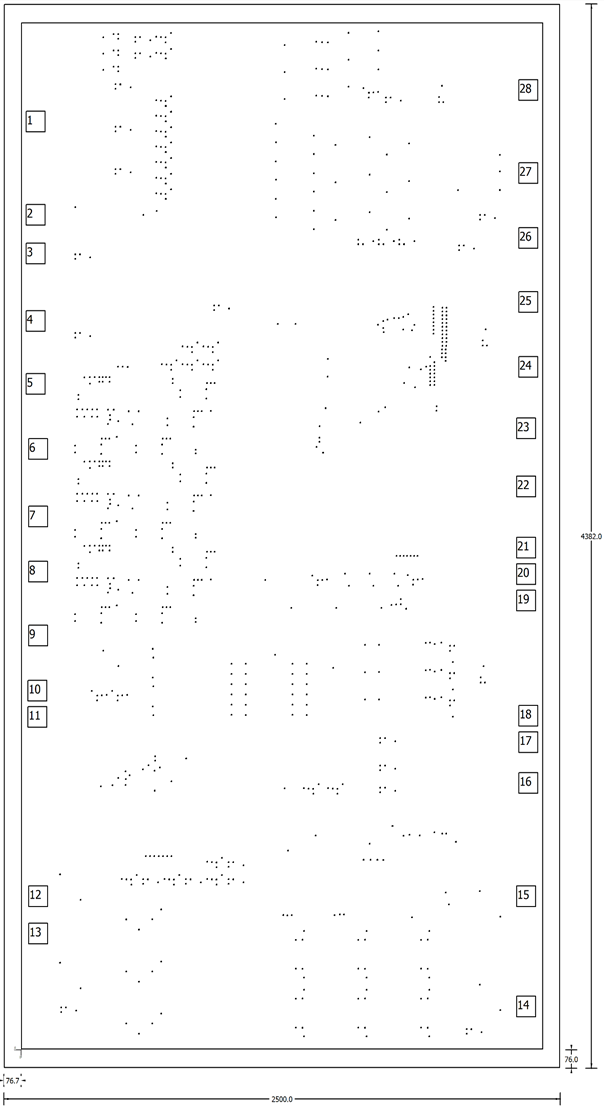

Figure 6-9 TPS7H500x-SP Bare Die Diagram -

Applicable for All Devices

Figure 6-9 TPS7H500x-SP Bare Die Diagram -

Applicable for All DevicesTable 6-3 TPS7H5001-SP Bond Pad Coordinates in

Microns

| DESCRIPTION | PAD NUMBER | X MIN | Y MIN | X MAX | Y MAX |

|---|---|---|---|---|---|

| RT | 1 | 21.33 | 3775.77 | 111.33 | 3865.77 |

| PS | 2 | 21.33 | 3392.37 | 111.33 | 3482.37 |

| SP | 3 | 21.33 | 3233.115 | 111.33 | 3323.115 |

| LEB | 4 | 21.33 | 2955.015 | 111.33 | 3045.015 |

| HICC | 5 | 21.33 | 2695.905 | 111.33 | 2785.905 |

| SYNC | 6 | 32.13 | 2427.705 | 122.13 | 2517.705 |

| DCL | 7 | 32.13 | 2149.515 | 122.13 | 2239.515 |

| NC | 8 | 32.175 | 1923.165 | 122.175 | 2013.165 |

| EN | 9 | 32.13 | 1660.275 | 122.13 | 1750.275 |

| VIN | 10 | 28.665 | 1432.53 | 118.665 | 1522.53 |

| VIN | 11 | 28.665 | 1325.475 | 118.665 | 1415.475 |

| OUTA | 12 | 32.13 | 586.755 | 122.13 | 676.755 |

| OUTB | 13 | 32.13 | 433.35 | 122.13 | 523.35 |

| SRB | 14 | 2224.62 | 132.93 | 2314.62 | 222.93 |

| SRA | 15 | 2224.62 | 586.755 | 2314.62 | 676.755 |

| AVSS | 16 | 2235.42 | 1053.315 | 2325.42 | 1143.315 |

| AVSS | 17 | 2235.42 | 1221.435 | 2325.42 | 1311.435 |

| AVSS | 18 | 2235.42 | 1330.425 | 2325.42 | 1420.425 |

| VLDO | 19 | 2224.62 | 1803.51 | 2314.62 | 1893.51 |

| VLDO | 20 | 2224.62 | 1912.545 | 2314.62 | 2002.545 |

| VLDO | 21 | 2224.62 | 2021.58 | 2314.62 | 2111.58 |

| CS_ILM | 22 | 2224.62 | 2274.3 | 2314.62 | 2364.3 |

| FAULT | 23 | 2224.62 | 2513.16 | 2314.62 | 2603.16 |

| REFCAP | 24 | 2235.42 | 2766.285 | 2325.42 | 2856.285 |

| RSC | 25 | 2235.42 | 3033.36 | 2325.42 | 3123.36 |

| SS | 26 | 2235.42 | 3296.655 | 2325.42 | 3386.655 |

| VSENSE | 27 | 2235.42 | 3563.64 | 2325.42 | 3653.64 |

| COMP | 28 | 2235.42 | 3905.55 | 2325.42 | 3995.55 |

Table 6-4 TPS7H5002-SP Bond Pad Coordinates in

Microns

| DESCRIPTION | PAD NUMBER | X MIN | Y MIN | X MAX | Y MAX |

|---|---|---|---|---|---|

| RT | 1 | 21.33 | 3775.77 | 111.33 | 3865.77 |

| PS | 2 | 21.33 | 3392.37 | 111.33 | 3482.37 |

| SP | 3 | 21.33 | 3233.115 | 111.33 | 3323.115 |

| LEB | 4 | 21.33 | 2955.015 | 111.33 | 3045.015 |

| HICC | 5 | 21.33 | 2695.905 | 111.33 | 2785.905 |

| SYNC | 6 | 32.13 | 2427.705 | 122.13 | 2517.705 |

| DCL | 7 | 32.13 | 2149.515 | 122.13 | 2239.515 |

| NC | 8 | 32.175 | 1923.165 | 122.175 | 2013.165 |

| EN | 9 | 32.13 | 1660.275 | 122.13 | 1750.275 |

| VIN | 10 | 28.665 | 1432.53 | 118.665 | 1522.53 |

| VIN | 11 | 28.665 | 1325.475 | 118.665 | 1415.475 |

| OUTA | 12 | 32.13 | 586.755 | 122.13 | 676.755 |

| NC | 13 | 32.13 | 433.35 | 122.13 | 523.35 |

| NC | 14 | 2224.62 | 132.93 | 2314.62 | 222.93 |

| SRA | 15 | 2224.62 | 586.755 | 2314.62 | 676.755 |

| AVSS | 16 | 2235.42 | 1053.315 | 2325.42 | 1143.315 |

| AVSS | 17 | 2235.42 | 1221.435 | 2325.42 | 1311.435 |

| AVSS | 18 | 2235.42 | 1330.425 | 2325.42 | 1420.425 |

| VLDO | 19 | 2224.62 | 1803.51 | 2314.62 | 1893.51 |

| VLDO | 20 | 2224.62 | 1912.545 | 2314.62 | 2002.545 |

| VLDO | 21 | 2224.62 | 2021.58 | 2314.62 | 2111.58 |

| CS_ILM | 22 | 2224.62 | 2274.3 | 2314.62 | 2364.3 |

| FAULT | 23 | 2224.62 | 2513.16 | 2314.62 | 2603.16 |

| REFCAP | 24 | 2235.42 | 2766.285 | 2325.42 | 2856.285 |

| RSC | 25 | 2235.42 | 3033.36 | 2325.42 | 3123.36 |

| SS | 26 | 2235.42 | 3296.655 | 2325.42 | 3386.655 |

| VSENSE | 27 | 2235.42 | 3563.64 | 2325.42 | 3653.64 |

| COMP | 28 | 2235.42 | 3905.55 | 2325.42 | 3995.55 |

Table 6-5 TPS7H5003-SP Bond Pad Coordinates in

Microns

| DESCRIPTION | PAD NUMBER | X MIN | Y MIN | X MAX | Y MAX |

|---|---|---|---|---|---|

| RT | 1 | 21.33 | 3775.77 | 111.33 | 3865.77 |

| NC | 2 | 21.33 | 3392.37 | 111.33 | 3482.37 |

| NC | 3 | 21.33 | 3233.115 | 111.33 | 3323.115 |

| NC | 4 | 21.33 | 2955.015 | 111.33 | 3045.015 |

| HICC | 5 | 21.33 | 2695.905 | 111.33 | 2785.905 |

| SYNC | 6 | 32.13 | 2427.705 | 122.13 | 2517.705 |

| DCL | 7 | 32.13 | 2149.515 | 122.13 | 2239.515 |

| NC | 8 | 32.175 | 1923.165 | 122.175 | 2013.165 |

| EN | 9 | 32.13 | 1660.275 | 122.13 | 1750.275 |

| VIN | 10 | 28.665 | 1432.53 | 118.665 | 1522.53 |

| VIN | 11 | 28.665 | 1325.475 | 118.665 | 1415.475 |

| OUTA | 12 | 32.13 | 586.755 | 122.13 | 676.755 |

| NC | 13 | 32.13 | 433.35 | 122.13 | 523.35 |

| NC | 14 | 2224.62 | 132.93 | 2314.62 | 222.93 |

| SRA | 15 | 2224.62 | 586.755 | 2314.62 | 676.755 |

| AVSS | 16 | 2235.42 | 1053.315 | 2325.42 | 1143.315 |

| AVSS | 17 | 2235.42 | 1221.435 | 2325.42 | 1311.435 |

| AVSS | 18 | 2235.42 | 1330.425 | 2325.42 | 1420.425 |

| VLDO | 19 | 2224.62 | 1803.51 | 2314.62 | 1893.51 |

| VLDO | 20 | 2224.62 | 1912.545 | 2314.62 | 2002.545 |

| VLDO | 21 | 2224.62 | 2021.58 | 2314.62 | 2111.58 |

| CS_ILM | 22 | 2224.62 | 2274.3 | 2314.62 | 2364.3 |

| FAULT | 23 | 2224.62 | 2513.16 | 2314.62 | 2603.16 |

| REFCAP | 24 | 2235.42 | 2766.285 | 2325.42 | 2856.285 |

| RSC | 25 | 2235.42 | 3033.36 | 2325.42 | 3123.36 |

| SS | 26 | 2235.42 | 3296.655 | 2325.42 | 3386.655 |

| VSENSE | 27 | 2235.42 | 3563.64 | 2325.42 | 3653.64 |

| COMP | 28 | 2235.42 | 3905.55 | 2325.42 | 3995.55 |

Table 6-6 TPS7H5004-SP Bond Pad Coordinates in

Microns

| DESCRIPTION | PAD NUMBER | X MIN | Y MIN | X MAX | Y MAX |

|---|---|---|---|---|---|

| RT | 1 | 21.33 | 3775.77 | 111.33 | 3865.77 |

| NC | 2 | 21.33 | 3392.37 | 111.33 | 3482.37 |

| NC | 3 | 21.33 | 3233.115 | 111.33 | 3323.115 |

| LEB | 4 | 21.33 | 2955.015 | 111.33 | 3045.015 |

| HICC | 5 | 21.33 | 2695.905 | 111.33 | 2785.905 |

| SYNC | 6 | 32.13 | 2427.705 | 122.13 | 2517.705 |

| DCL | 7 | 32.13 | 2149.515 | 122.13 | 2239.515 |

| NC | 8 | 32.175 | 1923.165 | 122.175 | 2013.165 |

| EN | 9 | 32.13 | 1660.275 | 122.13 | 1750.275 |

| VIN | 10 | 28.665 | 1432.53 | 118.665 | 1522.53 |

| VIN | 11 | 28.665 | 1325.475 | 118.665 | 1415.475 |

| OUTA | 12 | 32.13 | 586.755 | 122.13 | 676.755 |

| OUTB | 13 | 32.13 | 433.35 | 122.13 | 523.35 |

| NC | 14 | 2224.62 | 132.93 | 2314.62 | 222.93 |

| NC | 15 | 2224.62 | 586.755 | 2314.62 | 676.755 |

| AVSS | 16 | 2235.42 | 1053.315 | 2325.42 | 1143.315 |

| AVSS | 17 | 2235.42 | 1221.435 | 2325.42 | 1311.435 |

| AVSS | 18 | 2235.42 | 1330.425 | 2325.42 | 1420.425 |

| VLDO | 19 | 2224.62 | 1803.51 | 2314.62 | 1893.51 |

| VLDO | 20 | 2224.62 | 1912.545 | 2314.62 | 2002.545 |

| VLDO | 21 | 2224.62 | 2021.58 | 2314.62 | 2111.58 |

| CS_ILM | 22 | 2224.62 | 2274.3 | 2314.62 | 2364.3 |

| FAULT | 23 | 2224.62 | 2513.16 | 2314.62 | 2603.16 |

| REFCAP | 24 | 2235.42 | 2766.285 | 2325.42 | 2856.285 |

| RSC | 25 | 2235.42 | 3033.36 | 2325.42 | 3123.36 |

| SS | 26 | 2235.42 | 3296.655 | 2325.42 | 3386.655 |

| VSENSE | 27 | 2235.42 | 3563.64 | 2325.42 | 3653.64 |

| COMP | 28 | 2235.42 | 3905.55 | 2325.42 | 3995.55 |