JAJA708 September 2020 TPS55288 , TPS55288-Q1 , TPS552882 , TPS552882-Q1

2.2 昇降圧コンバータにおける広帯域 EMI の根本原因

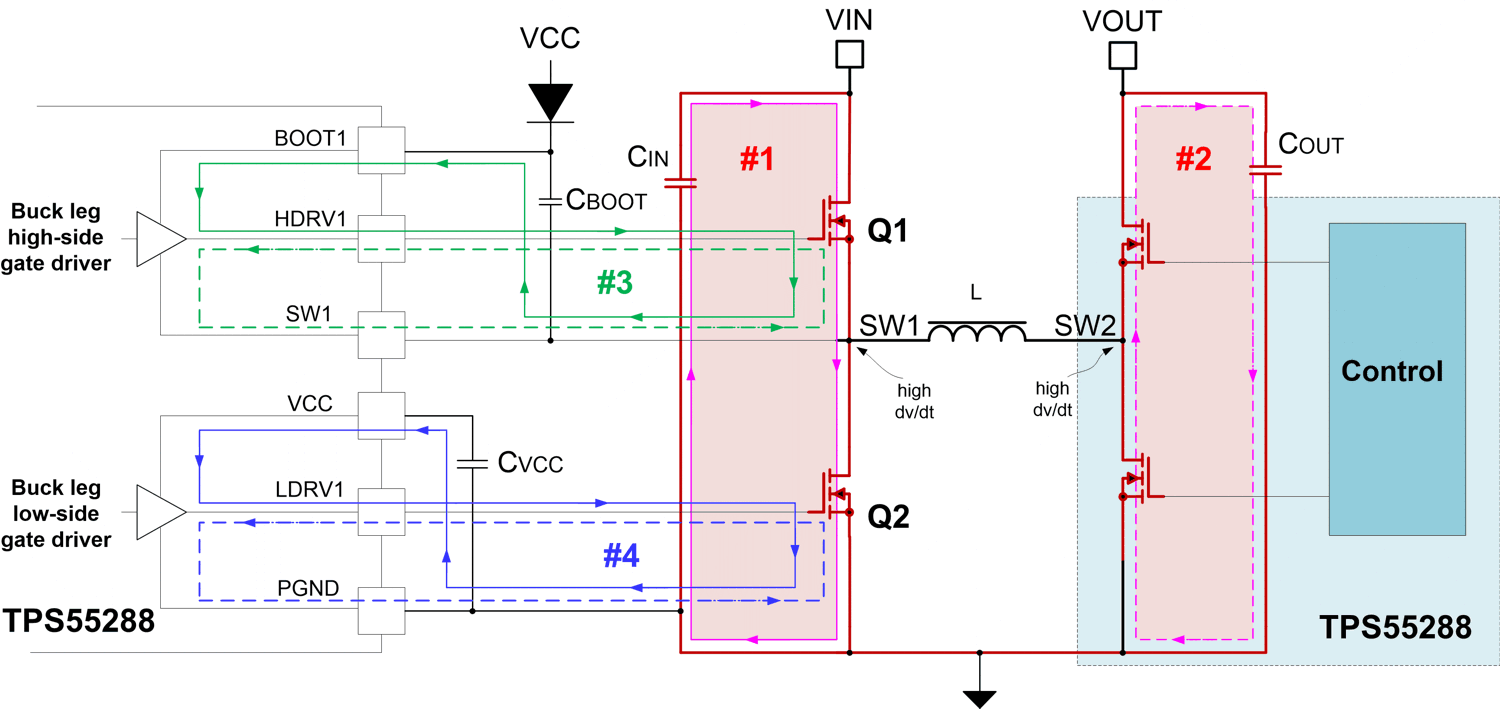

図 2-2 クリティカル・ループを持つ昇降圧コンバータの回路図

図 2-2 クリティカル・ループを持つ昇降圧コンバータの回路図出力段の部品、ゲート・ドライバ、VCC バイアス電源を内蔵したTPS55288 4 スイッチ昇降圧コンバータを、図 2-2 に示します。また図 2-2 には、大電流の配線、di/dt の大きいクリティカル・ループ、dv/dt の大きいスイッチング・ノードが色で示されています。

赤色の網で示されているのがループ 1 とループ 2 で、降圧レグと昇圧レグ用の 2 つのクリティカル高周波数電力ループです。これら 2 つのループの配線は長くて細いため、過剰なノイズ、スイッチング・ノードでのオーバーシュートとリンギング、寄生インダクタンスによるグランド・バウンスを引き起こす可能性があります。MOSFET のスイッチング・イベントでは、整流電流のスルーレートが 3~5A/ns を超える可能性があるため、2nH の寄生インダクタンスによって 6V の電圧スパイクが発生する可能性があります。これらのクリティカル・ループを流れるパルス電流方形波には、高調波成分が多いため、ループの面積が大きいと、放射エネルギーが大きくなり、電磁干渉の問題が発生する可能性があります。そのため、配線の長さと、ループ 1 およびループ 2 で囲まれた領域を最小化することが不可欠です。

図 2-2 のループ 3 と 4 は、降圧レグ MOSFET のゲート・ループです。ターンオンおよびターンオフ遷移中に MOSFET のゲート容量を充電および放電するために、最大で 1A 程度のピーク電流が短時間ゲート・ループを流れるため、干渉の問題も発生することがあります。このため、配線を行うときは、ループ 3 とループ 4 で囲まれる領域を最小限に抑えることも必要です。

ループ 1 とループ 2 は、最もクリティカルなループです。これらは電力ループ内にあるため、大きなパルス電力が発生します。これらの回路からは、直接の放射、隣接配線への干渉、および入力や出力のケーブルへの混入の可能性があり、重大な EMI の問題を引き起こす恐れがあります。

スイッチング・ノード SW1 と SW2 の最大電圧リンギングは、ループ 1 およびループ 2 のスイッチング速度とループ領域に対応します。ループ面積が大きいほど、スイッチング・ノードでの電圧リンギングが大きくなります。このリンギング周波数は、広帯域 EMI の中心の周波数範囲にも対応します。