JAJA708 September 2020 TPS55288 , TPS55288-Q1 , TPS552882 , TPS552882-Q1

2.3.4 スイッチング・ノードに RC スナバを追加する

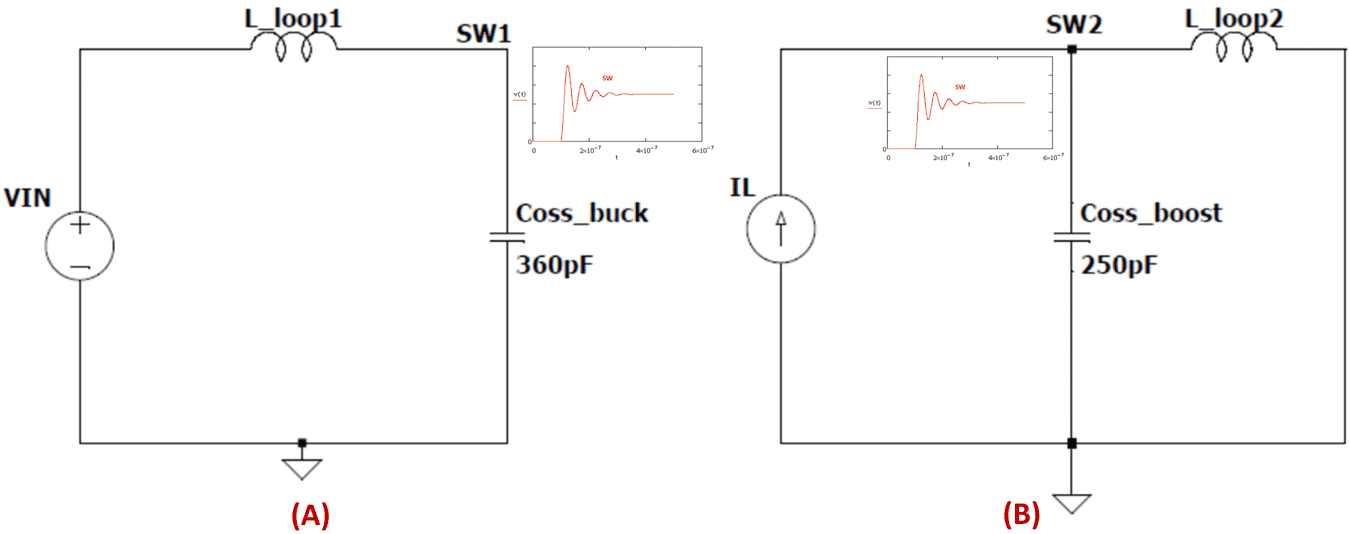

スイッチング・ループは、LC 回路としてモデル化できます。これは、入力側または出力側のデカップリング・コンデンサと、ハイサイドおよびローサイドの MOSFET によって形成されます。降圧レグ・スイッチング・ノード SW1 では、ハイサイド FET がオンでローサイド FET がオフのときにリンギングが発生します。昇圧レグ・スイッチング・ノード SW2 では、ローサイド FET がオフでハイサイド FET がオンのときにリンギングが発生します。この遷移状態でのスイッチング・ループの等価モデルを、図 2-10 に示します。

等価モデルのインダクタンス (L_loop1 および L_loop2) は、スイッチング・ループの合計ループ・インダクタンスに対応します。これには、PCB 配線のインダクタンス、デカップリング・コンデンサの ESL、MOSFET のパッケージ・インダクタンスが含まれます。ループの総容量は、ローサイド MOSFET の出力容量によって決定されます。したがって、スイッチング・ノードのリンギング周波数は、寄生ループ・インダクタンスとローサイド MOSFET の出力容量によって決定されます。与えられたスイッチング速度と MOSFET について、リンギングの最大振幅も寄生ループ・インダクタンスによって決定されます。

前の章で説明したように、スイッチング・ループの下にグランド・プレーンを追加するか、対称型 PCB レイアウトを使用すると、コンパクトな配置により寄生ループのインダクタンスを減らすことができます。ただし、実際のアプリケーションでは、部品の配置は PCB のサイズによって制限されます。

図 2-10 スイッチング・ループの等価モデル

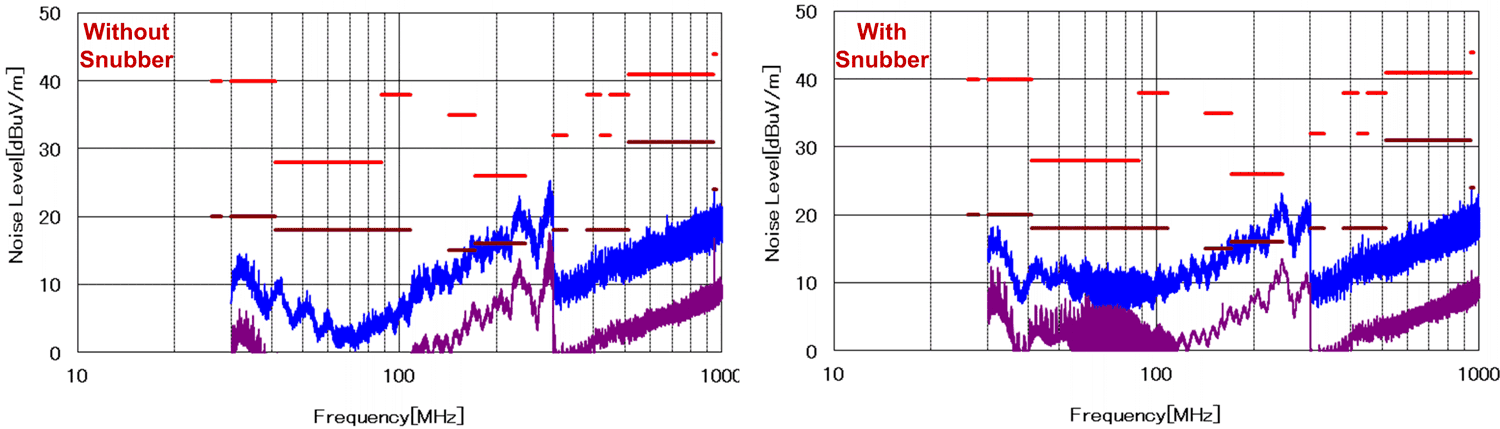

図 2-10 スイッチング・ループの等価モデル放射 EMI レベルが依然として要件レベルを超えており、これ以上レイアウトを改善できない場合はどうすればよいでしょうか。スイッチング・ノードと電源グランドとの間に RC スナバを追加すると、放射 EMI レベルを減らすために役立ちます。RC スナバは、スイッチング・ノードとグランド・プレーンのできるだけ近くに配置します。RC スナバありとなしで放射 EMI を比較した結果を、図 2-11 に示します。放射 EMI は、RC スナバにより 300MHz で約 6dBμV/m 改善されています。

図 2-11 RC スナバありとなしでの放射 EMI の比較

図 2-11 RC スナバありとなしでの放射 EMI の比較