SLAAEI9 December 2023 MSPM0C1103 , MSPM0C1103-Q1 , MSPM0C1104 , MSPM0C1104-Q1 , MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3105-Q1 , MSPM0G3106 , MSPM0G3106-Q1 , MSPM0G3107 , MSPM0G3107-Q1 , MSPM0G3505 , MSPM0G3505-Q1 , MSPM0G3506 , MSPM0G3506-Q1 , MSPM0G3507 , MSPM0G3507-Q1 , MSPM0L1105 , MSPM0L1106 , MSPM0L1228

- 1

- Abstract

- Trademarks

- 1MSPM0 Portfolio Overview

-

2Ecosystem And Migration

- 2.1 Ecosystem Comparison

- 2.2 Migration Process

- 2.3 Example

- 3Core Architecture Comparison

- 4Digital Peripheral Comparison

- 5Analog Peripheral Comparison

3.3 Power UP and Reset Summary and Comparison

Both STM8 devices and MSPM0 devices have the minimum operating voltage and have modules in place to make sure that the device starts up properly by holding the device or portions of the device in a reset state. Table 3-5 shows a comparison on how this is done between the two families and what modules control the power up process and reset across the families.

| STM8 | MSPM0 | ||

|---|---|---|---|

| Power-On Reset (POR) | Rise detection: VDD>VPOR, POR state is released, BOR starts to work. | Power-On Reset (POR) | Rise detection: VDD>POR+, POR

state is released, and bandgap reference and BOR is started Fall detection: VDD<POR-, device is held in POR state |

| Power-Down Reset (PDR) | Fall detection: VDD<VPDR, PDR keeps the device under reset. | ||

| Brownout Reset (BOR)(1) | Rise detection:

VDD>VBOR+, BOR state is released,

device continues the boot process. Fall detection: VDD<VBOR-, BOR state is generated. BOR has five different levels to be selected. |

Brownout Reset (BOR)- 0 level(2) | Rise detection: VDD>BOR0+, Device continues the boot process, and PMU is started Fall detection: VDD<BOR0-, Device is held in BOR state. |

| Brownout Reset (BOR)- 1 to 3 level(2) | Fall detection: 1) VDD<BORx- (x=1, 2, 3), an interrupt request is generated, and the BOR circuit automatically switches the BOR threshold level to BOR0. 2) VDD<BOR0-, Device is held in BOR state |

||

| Programmable voltage detector (PVD)(3) | Rise detection: VDD>VPVD, a PVD

event is genrated. Fall detection: VDD<VPVD, a PVD event is genrated. PVD has seven different levels to be selected. |

N/A | N/A |

| RTC Reset | RTC and associated registers are reset through system reset or power-on reset. | RTC Reset | RTC and associated clocks are reset through BOOTRST, BOR, or POR |

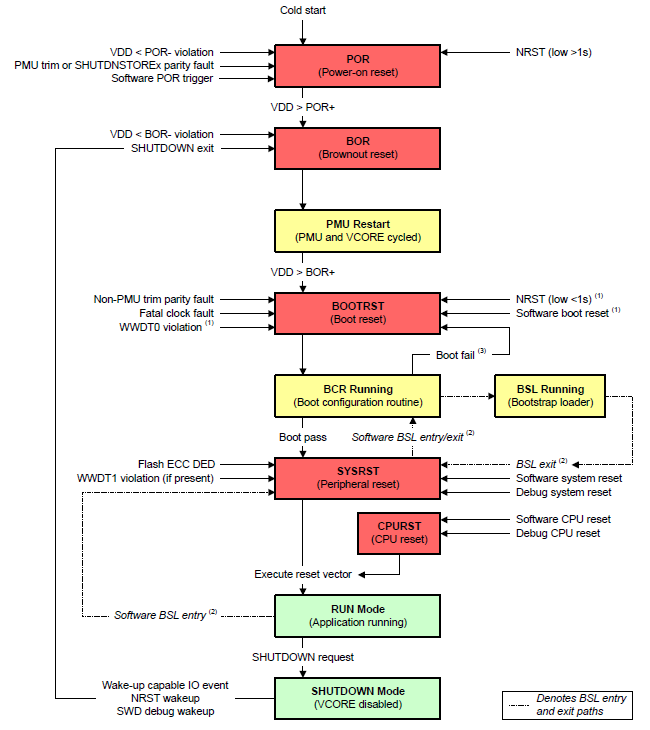

Figure 3-1 shows the MSPM0 Reset function. MSPM0 devices have five reset levels: Power-on reset (POR), Brownout reset (BOR), Boot reset (BOOTRST), System reset (SYSRST) and CPU reset (CPURST).

Figure 3-1 MSP Reset Function

Figure 3-1 MSP Reset Function