SNLA433 august 2023 DS320PR1601 , DS320PR410 , DS320PR810 , SN75LVPE5412 , SN75LVPE5421

2.4 Redriver EQ Tuning

In most cases, PCIe Gen5 redrivers require tuning the CTLE setting to provide satisfactory eye openings. The recommendation is to leave DC gain at the default setting of 0 dB. Refer to PCI Express Compliance Testing with the DS320PR810 for direct effects of DC gain and equalization settings.

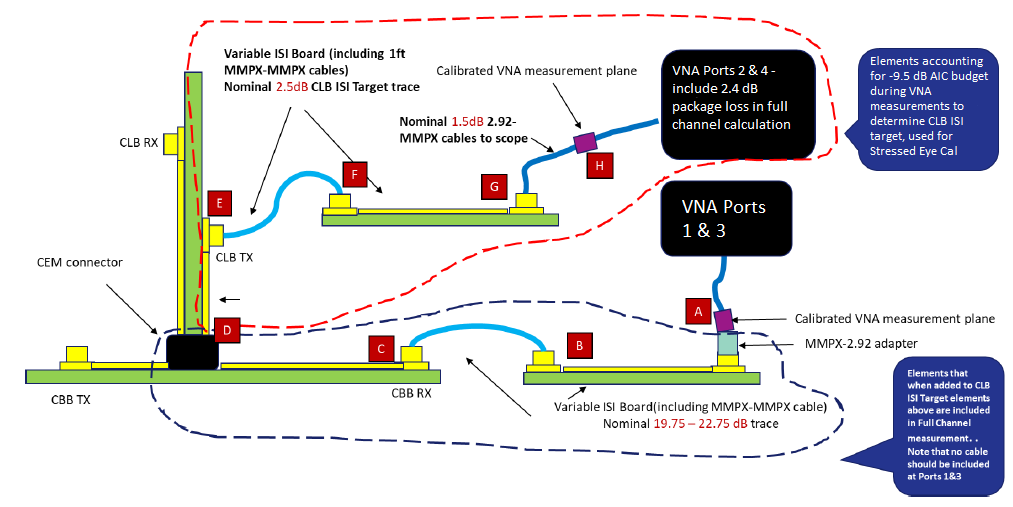

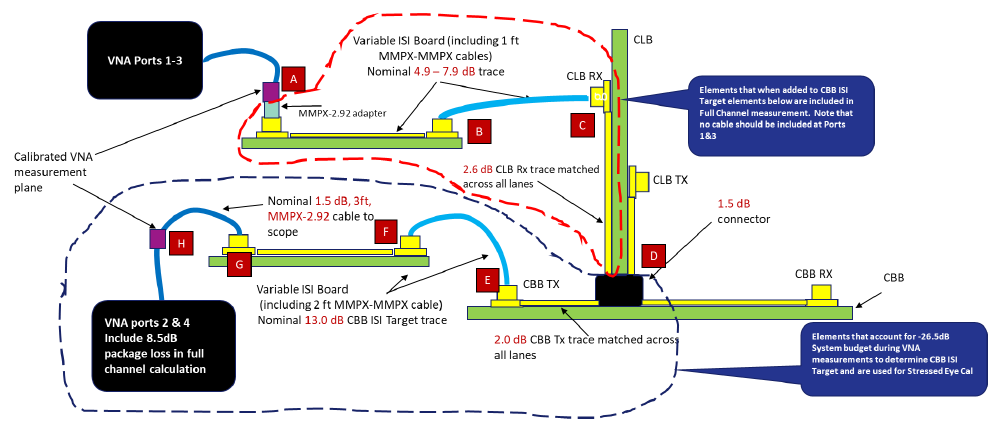

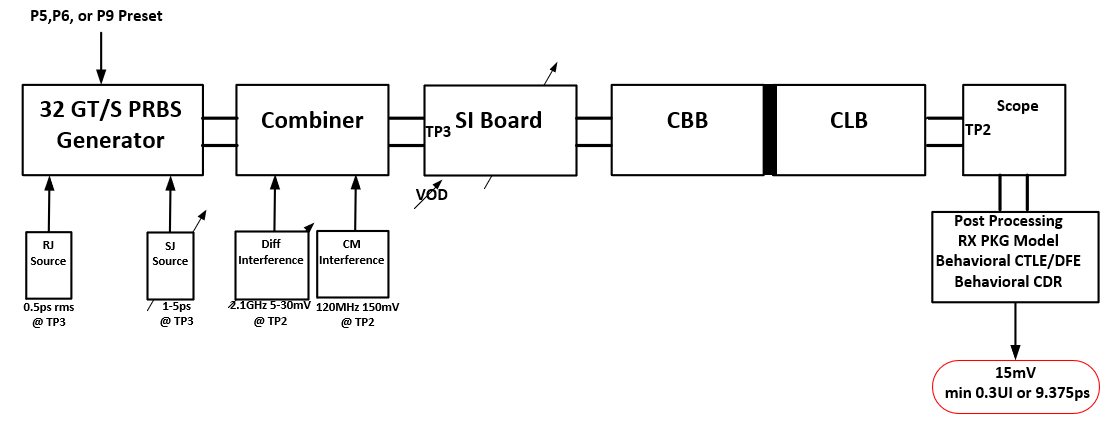

Receiver link equalization compliance is done on system or Add-In-Cards to verify interoperability at 1E-12 under stressed conditions. First, different parameters calibration is done to provide the same environment for different systems or AIC applications. The following setups are used for the RX EQ compliance adherence. Images are courtesy of PCI-SIG.

Figure 2-7 PCI-SIG AIC RX Calibration Specifications

Figure 2-7 PCI-SIG AIC RX Calibration Specifications Figure 2-8 PCI-SIG System RX Calibration Specifications

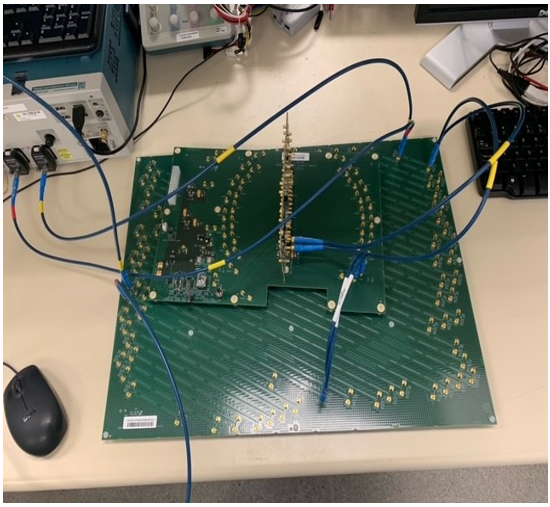

Figure 2-8 PCI-SIG System RX Calibration Specifications Figure 2-9 PCIe Gen5 SI, CBB, and CLB Boards

Figure 2-9 PCIe Gen5 SI, CBB, and CLB Boards Figure 2-10 RX Compliance Block Diagram

Figure 2-10 RX Compliance Block Diagram