SPRACZ0A August 2021 – March 2023 F29H850TU , F29H850TU , F29H859TU-Q1 , F29H859TU-Q1 , TMS320F2800132 , TMS320F2800132 , TMS320F2800133 , TMS320F2800133 , TMS320F2800135 , TMS320F2800135 , TMS320F2800137 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280023C , TMS320F280025 , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280033 , TMS320F280034 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C , TMS320F280049C-Q1 , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28076 , TMS320F28374D , TMS320F28374D , TMS320F28374S , TMS320F28374S , TMS320F28375D , TMS320F28375D , TMS320F28375S , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376D , TMS320F28376S , TMS320F28376S , TMS320F28377D , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378D , TMS320F28378S , TMS320F28378S , TMS320F28379D , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28379S , TMS320F28384D , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388D , TMS320F28388S , TMS320F28388S , TMS320F28P550SG , TMS320F28P550SG , TMS320F28P550SJ , TMS320F28P550SJ , TMS320F28P559SJ-Q1 , TMS320F28P559SJ-Q1 , TMS320F28P650DH , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1 , TMS320F28P659SH-Q1

- Abstract

- Trademarks

-

1Introduction

- 1.1

Resources

- 1.1.1 TINA-TI SPICE-Based Analog Simulation Program

- 1.1.2 PSPICE for TI Design and Simulation Tool

- 1.1.3 Application Report: ADC Input Circuit Evaluation for C2000 MCUs

- 1.1.4 TI Precision Labs - SAR ADC Input Driver Design Series

- 1.1.5 Analog Engineer's Calculator

- 1.1.6 TI Precision Labs - Op Amps: Stability Series

- 1.1.7 Related Application Reports

- 1.1.8 Comparison of Schematic Capture and Simulation Tools

- 1.1.9 PSpice for TI ADC Input Models

- 1.1

Resources

-

2Charge-Sharing Concept

- 2.1 Traditional High-Speed ADC Driving Circuits

- 2.2 Increased Cs in High-Speed ADC Driving Circuits

- 2.3 Very Large Cs in ADC Driving Circuits

- 2.4 Charge-Sharing Operation

- 2.5 Sample Rate and Source Impedance vs. Tracking Error

- 2.6 Analytical Solution to Tracking Error

- 2.7 Charge-Sharing in Multiplexed ADCs

- 2.8 Charge-Sharing Circuit Advantages

- 2.9 Charge-Sharing Circuit Disadvantages

- 3Charge Sharing Design Flow

- 4Charge-Sharing Circuit Simulation Methods

- 5Example Circuit Designs

- 6Summary

- A Appendix: ADC Input Settling Motivation

- References

- Revision History

4.2 Configure the Simulation Parameters

The primary configuration that needs to be done for charge-sharing simulations is to set the sample rate. This is controlled by settings of the piecewise linear voltage sources tacq and tdis. The secondary configuration of PSpice for TI simulation parameters is also necessary to optimize simulation results.

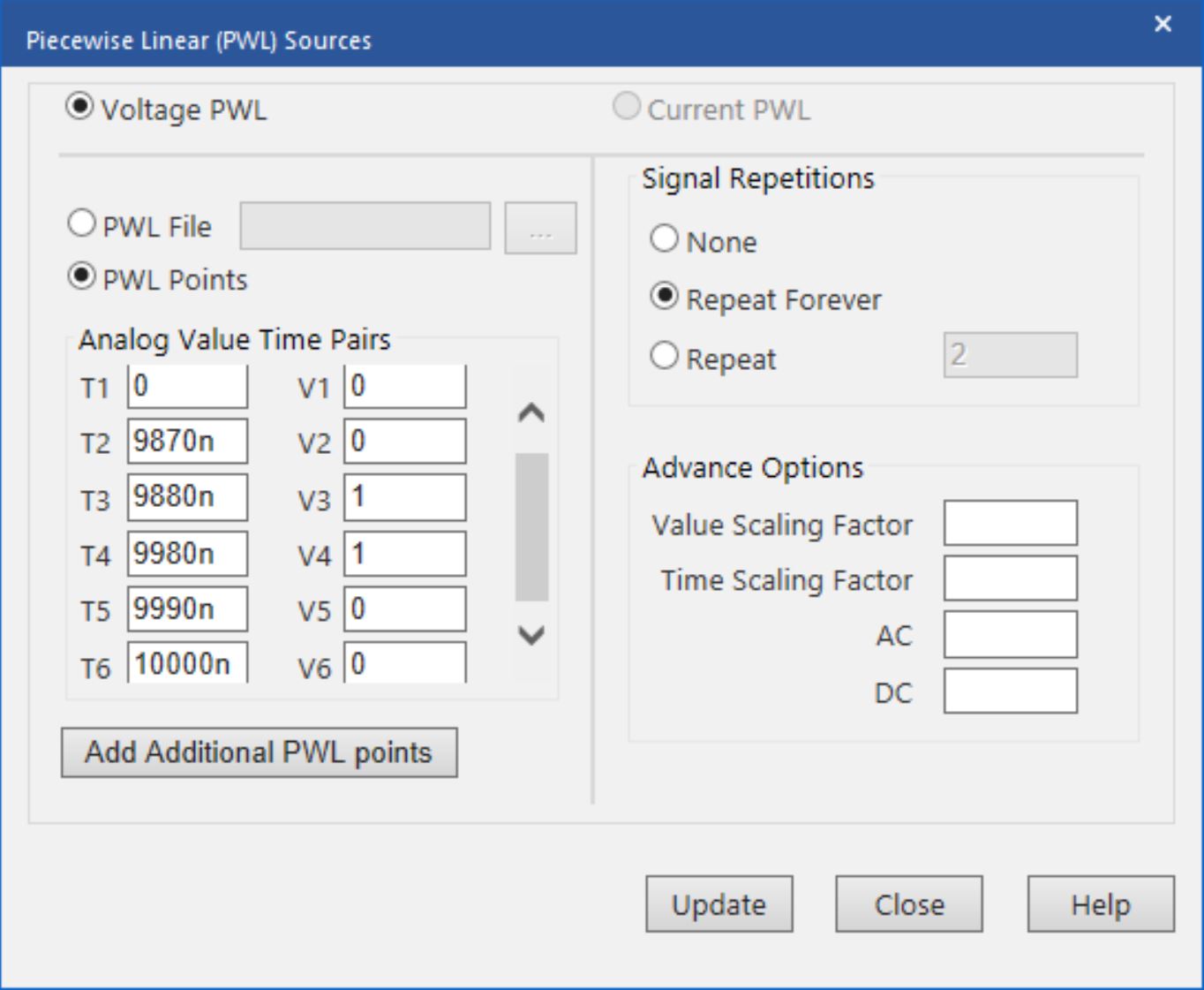

Sample tacq timing configurations for a 100 ns acquisition window and 100kHz sampling are shown in Figure 4-3. The first four lines configure the S+H window to occur from 0 to 102 ns with 1 ns rise and fall times. The last line (which is of primary interest) configures how often the waveform repeats. This effectively sets the sample rate, so 10000 ns (10 µs) is equivalent to 100 kHz sampling.

Figure 4-3 Example Timings for

tacq (Piecewise Linear)

Figure 4-3 Example Timings for

tacq (Piecewise Linear)Sample tdis timing configurations for a 100 ns discharge period and 100 kHz sampling are shown in Figure 4-4. The first five lines specify a 100 ns discharge period with 10ns rise and fall times starting at 9.87 µs. The last line configures how often the waveform repeats. This effectively sets the sample rate, so 10000 ns (10 µs) is equivalent to 100 kHz sampling. Ensure that the last line of the tdis and tacq timings always exactly match! It is not necessary for this discharge period to occur exactly at the end of the triggering period, so it is acceptable to change the sampling rate by only changing the last line. For example, changing the final line of both tdis and tacq to 20000 ns will change the sample rate to 50 kHz. Do, however, ensure that the discharge period does not overlap with the S+H period in tacq as this will result in the input being shorted to ground instead of charging CH.

Figure 4-4 Example Timings for

tdis (Piecewise Linear)

Figure 4-4 Example Timings for

tdis (Piecewise Linear)Note that the timings are configured to emulate conversions triggered at 100 kHz frequency. This slower sample rate on a specific channel is typical of a charge-sharing input design (instead of back-to-back continuous conversions at the max ADC sample rate). The triggering rate can be modified to match the actual application ePWM trigger rate by modifying the period of the tacq and tdis timing sources. Do, however, ensure that the trigger rate is slower than the total acquisition time plus ADC conversion time. The ADC conversion time can be found in the device-specific data manual table "ADC Timings".

When a simulation is run, the PSpice for TI simulation parameters also need to be configured for maximum accuracy. To increase the numeric precision of bias point simulation results, go to PSpice ➔ Bias Points ➔ Preferences... and increase the Displayed Precision parameter. To optimize transient simulation results, open the transient simulation profile and decrease the maximum step size. To increase the numeric precision of simulation results in the PSpice for TI simulation window, go to Tools ➔ Options... ➔ Cursor Settings and increase the number of cursor digits.

This application report requires precision on the level of microvolts. For this reason, ensure that the Displayed Precision parameter and number of cursor digits are greater than or equal to 7. The maximum step size is configured on a simulation-by-simulation basis, but a maximum step size that is three to four orders of magnitude smaller than the simulation stop time is generally sufficient.