SLAAE75A November 2022 – March 2023 MSPM0L1105 , MSPM0L1106 , MSPM0L1227 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L1303 , MSPM0L1304 , MSPM0L1304-Q1 , MSPM0L1305 , MSPM0L1305-Q1 , MSPM0L1306 , MSPM0L1306-Q1 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346 , MSPM0L2227 , MSPM0L2228 , MSPM0L2228-Q1

2.1 Digital Power Supply

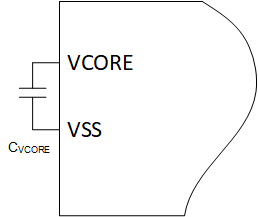

VCORE Regulator

There is an internal low-dropout linear voltage regulator to generate a 1.35-V supply rail to power the device core. In general, the core regulator output (VCORE) supplies power to the core logic, which includes the CPU, digital peripherals and the device memory. The core regulator requires an external capacitor (CVCORE) which is connected between the device VCORE pin and VSS (ground) (see #GUID-13FB8421-B5DF-4D50-92BB-3A11E8DFDE90). See the device-specific data sheet for the correct value and tolerance of CVCORE. CVCORE should be placed close to the VCORE pin.

The core regulator is active in all power modes except for SHUTDOWN. In all other power modes (RUN, SLEEP, STOP, and STANDBY) the drive strength of the regulator is configured automatically to support the max load current of each mode. This reduces the quiescent current of the regulator when using low power modes, improving low power performance.

Figure 2-1 VCORE Regulator Circuit

Figure 2-1 VCORE Regulator Circuit