SLAAE75A November 2022 – March 2023 MSPM0L1105 , MSPM0L1106 , MSPM0L1227 , MSPM0L1227-Q1 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L1303 , MSPM0L1304 , MSPM0L1304-Q1 , MSPM0L1305 , MSPM0L1305-Q1 , MSPM0L1306 , MSPM0L1306-Q1 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346 , MSPM0L2227 , MSPM0L2227-Q1 , MSPM0L2228 , MSPM0L2228-Q1

8.4 Open-Drain GPIOs Enable 5-V Communication Without a Level Shifter

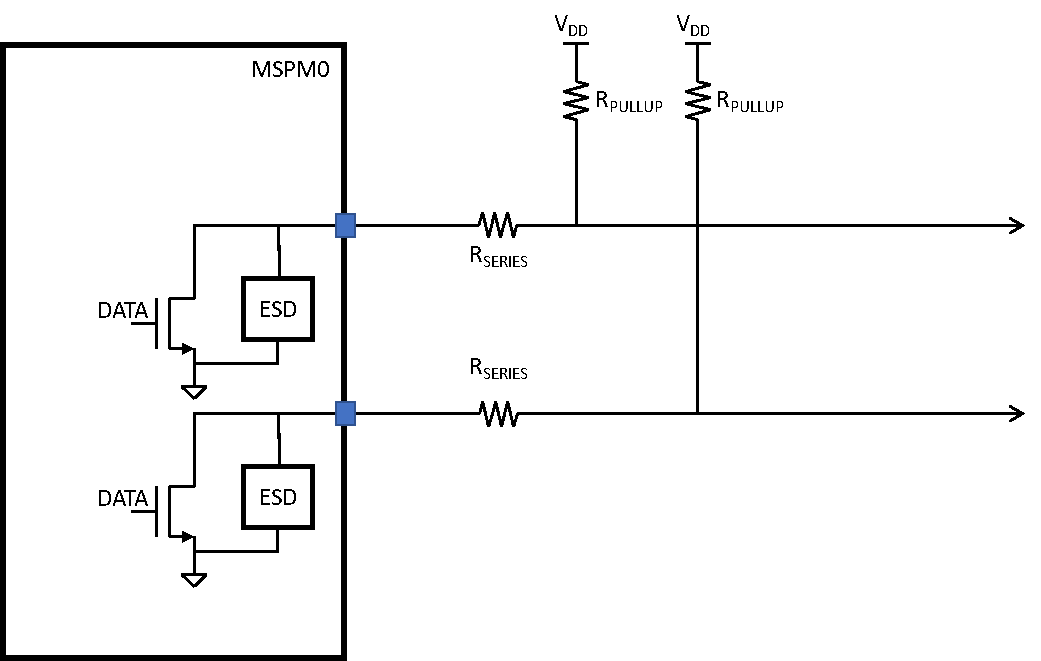

ODIO are tolerant to 5-V input. Because they are open drain, an external pullup resistor is needed for the pin to be able to output high. This I/O can used for UART or I2C interface with different voltage levels. To limit the current, a series resistor must be placed between the pin and the pullup resistor, and the RSERIES must be no less than 250 Ω. As shown in #GUID-290D6907-E05F-472B-8C10-A6AA74A1ADA5, TI recommends 270 Ω. The value of the pullup resistor depends on the output frequency (see GUID-65EEBB28-5EBC-4AD3-9013-73ABE445E75C.html).

Figure 8-1 Suggested ODIO Circuit

Figure 8-1 Suggested ODIO Circuit