JAJT348 September 2024 TPS62912 , TPS62913 , TPS7A52 , TPS7A53 , TPS7A54 , TPS7A84 , TPS7A94 , TPSM82912 , TPSM82913

医療用アプリケーション、試験 / 測定、ワイヤレス インフラなどの分野には、クロック、データ コンバータ、アンプを使用し、ノイズの影響を受けやすいシステムが多く存在します。それらのシステム向けの電源を設計するエンジニアは、精度の向上や、システム ノイズの最小化という共通の課題に直面します。「ノイズ」という用語は人によって意味が異なりますが、この記事では、「回路内の抵抗とトランジスタが生成する低周波数の熱ノイズ」を「ノイズ」と定義します。ノイズは、平方根ヘルツあたりのマイクロボルト単位のスペクトル ノイズ密度曲線により、また 2 乗平均平方根マイクロボルト単位の積分出力ノイズとして確認することができ、一般的に 10Hz ~ 100kHz の特定の範囲にわたります。電源内のノイズは、A/D コンバータの性能低下や、クロックのジッタ発生につながる可能性があります。

クロック、データ コンバータ、アンプに電力を供給する場合、従来の構成では、図 1 に示すように最初の段で DC/DC コンバータ (またはモジュール) を使用し、その後段に LDO (低ドロップアウト) レギュレータ、さらにその後段にフェライト ビーズ フィルタを配置します。LDO の例は、TPS7A94、TPS7A82、TPS7A84、TPS7A52、TPS7A53、TPS7A54 などです。この設計のやり方で、電源からのノイズとリップルの両方を最小化でき、負荷電流がおおむね 2A 以下の場合は適切に動作します。ただし、負荷が大きくなるほど、LDO で生じる電力損失が原因で、効率と放熱管理に課題が生じます。たとえば、標準的なアナログ フロント エンド アプリケーションでは、ポスト (後段) レギュレーション LDO により電力損失が 1.5W 増加する可能性があります。設計のために低ノイズで効率の良い方法を探している方々もいるでしょうが、他の選択肢があるかもしれません。

図 1 DC/DC コンバータ、LDO、フェライト ビーズ フィルタを使用する標準的な低ノイズ アーキテクチャ

図 1 DC/DC コンバータ、LDO、フェライト ビーズ フィルタを使用する標準的な低ノイズ アーキテクチャLDO の代わりに低ノイズの降圧コンバータまたは降圧モジュールを採用

電力損失を管理する方法の 1 つは、LDO で生じるドロップアウトを最小化することです。ただし、このアプローチは、ノイズ特性に悪影響を及ぼすことになります。加えて、より多くの電流を供給できる LDO は通常、より大型であり、設計のフットプリントやコストの増加につながります。電力損失を制御しながら低ノイズを確保する効果的な方法は、図 2 に示すように LDO を電源設計から全面的に排除し、低ノイズの DC/DC 降圧コンバータまたは降圧モジュールを使用することです。

図 2 LDO なしで低ノイズ降圧コンバータを採用

図 2 LDO なしで低ノイズ降圧コンバータを採用この構想を目にすると、ノイズを低減する重要なデバイスを取り除いて、どのように低ノイズの電力を供給するのかと疑問に思うでしょう。多くの LDO には、エラー アンプへのノイズを最小限に抑えるために、バンドギャップ リファレンスにローパス フィルタがあります。TPS62912 と TPS62913 で構成される低ノイズ降圧コンバータ ファミリや、TPSM82912 と TPSM82913 の各モジュールは、ノイズ低減 / ソフト スタート ピンを実装しており、ここに 1 個のコンデンサを接続して、図 3 に示すように、内蔵の Rf と、外部接続の CNR/SS を組み合わせてローパス RC フィルタを形成します。この実装は本質的に、LDO 内に存在するバンドギャップ ローパス フィルタの挙動を模倣したものです。TPS62913 または TPSM82913 で実現できる範囲よりいっそうの低ノイズが必要な場合、TPS7A94 のような低ノイズ LDO を採用できます。この製品には、ドロップアウトの低減や、消費電力の低減という特長があり、しかも超低ノイズを実現できます。これについては、アプリケーション ブリーフ SBVA099 で詳細に説明しています。

図 3 バンドギャップ ノイズ フィルタリングを実施する低ノイズ降圧回路の図

図 3 バンドギャップ ノイズ フィルタリングを実施する低ノイズ降圧回路の図出力電圧リップルの対策

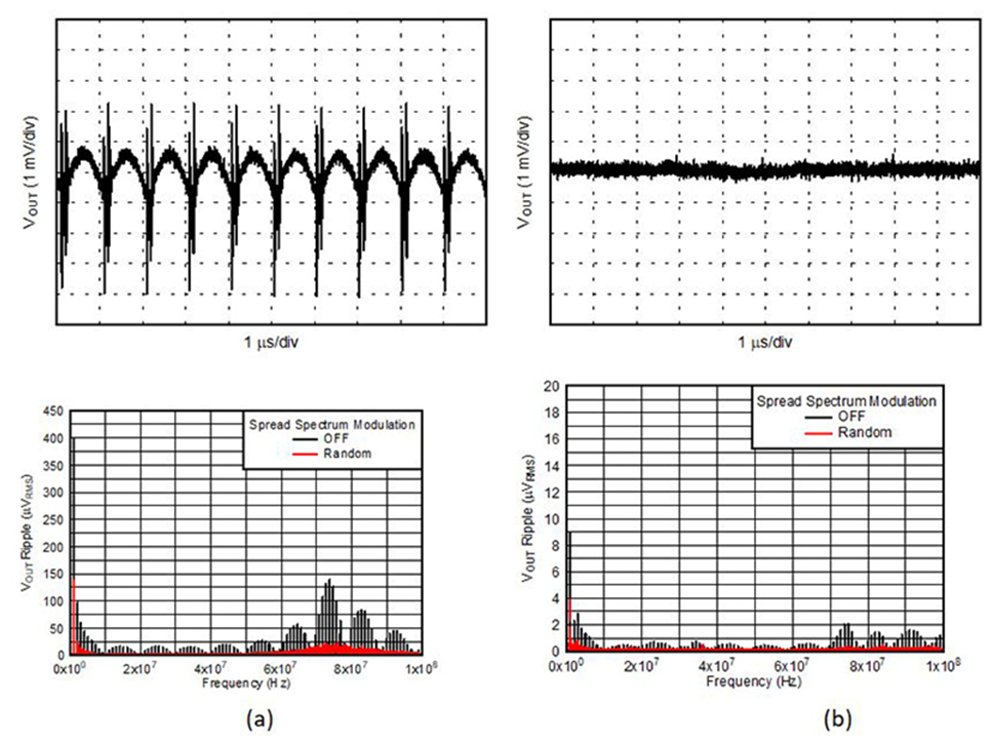

どの DC/DC コンバータでも、使用するスイッチング周波数と同じ周波数で出力電圧リップルが生じます。高精度システム内にある、ノイズに敏感なアナログ電源レールは、スペクトル内での周波数スプリアスを最小化するために、リップルが最小の電源電圧を必要とします。この周波数スプリアスは通常、DC/DC コンバータのスイッチング周波数、インダクタの値、出力容量、等価直列抵抗、等価直列インダクタンスによって異なります。これらの部品に起因するリップルを低減するために、エンジニアは多くの場合、LDO を使用するか、または小型フェライト ビーズとコンデンサを組み合わせて π (パイ) フィルタを形成することで (あるいはその両方で)、負荷側でリップルを最小化します。TPS62912 と TPS62913 のような低リップル降圧コンバータや、TPSM82913 モジュールは、フェライト ビーズ補償とリモート センス フィードバック機能を内蔵することで、このフェライト ビーズ フィルタを活用します。このフェライト ビーズのインダクタンスに追加の出力コンデンサを組み合わせることで、出力電圧リップルのうち高周波成分を除去しています。その結果、図 4 に示すように、リップルを約 30dB 低減できます。

図 4 フェライト ビーズ フィルタの前 (a) と後 (b) の出力電圧リップル

図 4 フェライト ビーズ フィルタの前 (a) と後 (b) の出力電圧リップルまとめ

低ノイズ降圧コンバータは、システムのノイズやリップルを低減する機能を統合しているので、後段 LDO を使用せずに低ノイズの電源ソリューションを製作するのに役立ちます。当然ながら、求められるノイズ レベルはアプリケーションごとに異なり、出力電圧が変われば必要な性能も異なるので、自身の設計にベストな低ノイズ アーキテクチャを判断できるのは設計者だけです。しかし、ノイズの影響を受けやすいアナログ電源の設計を簡素化し、電力損失を減らして、設計全体のフットプリントを縮小したい場合は、低ノイズ降圧コンバータの使用をご検討ください。

その他の資料

- 『リップルとノイズの低い降圧コンバータ TPS62913 を使用して、影響を受けやすい ADC 設計に電力を供給』

- 『リップルとノイズの低い降圧コンバータ TPS62913 を使用して AFE7920 に電力を供給』

- DC/DC コンバータを使用する際の出力電圧リップルへの影響の詳細については、技術記事『降圧レギュレータの出力リップルに関する理解と管理』をご覧ください。

- TPS62913 と TPS62913 を活用してノイズとリップルを低減する方法については、トレーニング ビデオ『低リップルで低静止電流の DC/DC ポイント オブ ロード降圧コンバータ』をご覧ください。

- 降圧コンバータに起因する出力電圧リップルを低減する他の方法については、ホワイト ペーパー『LDO を使用せずに高効率かつ低消費電力の電源を製作するのに役立つ低ノイズと低リップルの手法』をご覧ください。

商標

すべての商標はそれぞれの所有者に帰属します。