SLAU887 February 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3105-Q1 , MSPM0G3106 , MSPM0G3106-Q1 , MSPM0G3107 , MSPM0G3107-Q1 , MSPM0G3505 , MSPM0G3505-Q1 , MSPM0G3506 , MSPM0G3506-Q1 , MSPM0G3507 , MSPM0G3507-Q1 , MSPM0L1105 , MSPM0L1106 , MSPM0L1227 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L1303 , MSPM0L1304 , MSPM0L1304-Q1 , MSPM0L1305 , MSPM0L1305-Q1 , MSPM0L1306 , MSPM0L1306-Q1 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346 , MSPM0L2227 , MSPM0L2228 , MSPM0L2228-Q1

- Abstract

- Trademarks

- 1Overview of BSL Features

- 2Terminology

- 3BSL Architecture

- 4Bootloader Protocol

- 5Sample Program Flow with Bootloader

- 6Secondary Bootloader

- 7Interface Plug-in

- 8References

- 9Revision History

3.2.3 GPIO Based Invocation

GPIO used for BSL invocation can be configured in the BSL Configuration TRM in Non-main memory.

Fresh devices will have the TI programmed default pin detail in BSL configuration.

GPIO pin based invocation can be disabled in the BCR configuration. It is enabled by default.

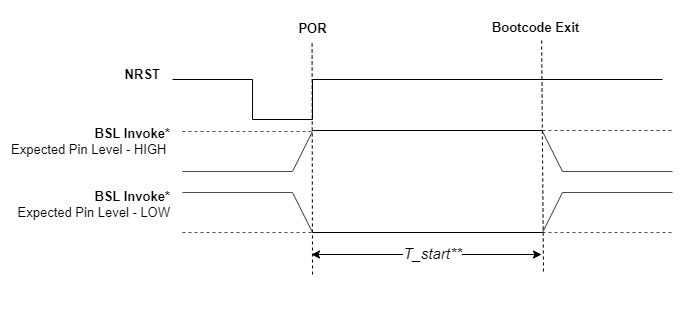

GPIO should be asserted before the POR, and the state should be maintained for at-least T_start ms after POR. Then the GPIO pin state can be de-asserted.

Figure 3-2 Invocation From GPIO

Figure 3-2 Invocation From GPIO* - GPIO pin to be used as 'BSL Invoke' and 'Expected Pin Level' can be configured in BSL configuration

** - T_start refers to the Cold boot startup time, specified in the device specific data sheet