JAJA784 December 2022 AMC1202 , AMC1302 , AMC1306M05 , AMC22C11 , AMC22C12 , AMC23C10 , AMC23C11 , AMC23C12 , AMC23C14 , AMC23C15 , AMC3302 , AMC3306M05

3.3 ポイント G - DC/DC タンク電流センシング

このセクションでは、スイッチング タンクであるポイント G での電流センシング要件について詳しく説明します。共振 CLLLC 双方向絶縁型 DC/DC コンバータでは、同期整流にゼロクロス検出 (ZCD) が必要です。これによって、導通損失が低減され、システム効率が向上します。

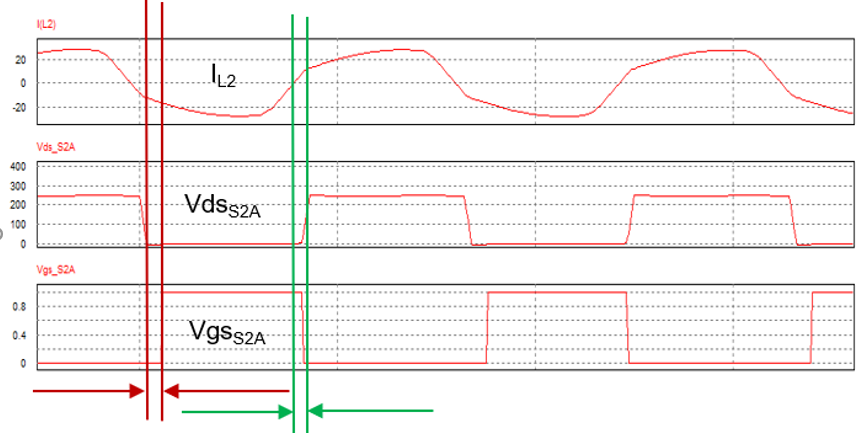

図 3-6 絶縁型 DC/DC コンバータの 1 次側タンクまたは 2 次側タンクでの電流センシング

図 3-6 絶縁型 DC/DC コンバータの 1 次側タンクまたは 2 次側タンクでの電流センシング図 3-6 では、2 本の緑色のカーソル線で、ゼロクロスから 2 次側 FET ターンオンまでの伝搬遅延を示しています。

図 3-7 ゼロクロス検出の伝搬遅延

図 3-7 ゼロクロス検出の伝搬遅延CLLLC トポロジでの ZCD 回路の最新の実装は、共振コンデンサと直列に、電流トランス (CT) またはロゴスキー コイルを 1 次側と 2 次側に配置することです。CT またはロゴスキー コイルによるアプローチにおける一般的な伝搬遅延は、100ns~200ns です。この遅延は CLLLC トポロジに大きな損失を引き起こし、DC/DC コンバータの全体的な効率に負の影響を及ぼす可能性があります。ピーク電流が約 30A、共振スイッチング周波数が 500kHz、ターンオン遅延が 100ns であると想定すると、FET がオンになるまで、ボディ ダイオード (順方向電圧 4.5V) が 9.3A を流します。これにより、FET あたりのピーク時のエネルギー損失は 約 42W になります。

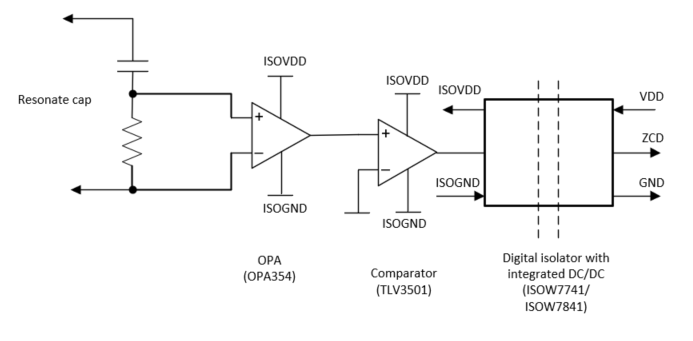

図 3-8 は別のアプローチです。ここでは、共振コンデンサ電圧と微分回路を組み合わせて実装し、正弦波電流を再現しています。再現された正弦波信号は、さらに差動からシングルエンドへの OPA (OPA354) と ZCD 用高速コンパレータ (TLV3501) によって処理されます。

図 3-8 ISOW7741、ISOW7841 を使用した ZCD 回路

図 3-8 ISOW7741、ISOW7841 を使用した ZCD 回路ゼロクロス信号は、デジタル アイソレータ (ISOW7741 または ISOW7841) によって絶縁されます。これらのデジタル アイソレータは、OPA デバイスとコンパレータ デバイス用の絶縁電源を生成する絶縁型 DC/DC コンバータを内蔵しています。OPA354、TLV3501、ISOW7741 の伝搬遅延はそれぞれ 0.6ns、4.5ns、10.7ns で、設計全体の合計伝搬遅延は 15.8ns となり、CT またはロゴスキー コイルによるアプローチの約 1/10 になります。前の例と同じスイッチング周波数とピーク電流を想定すると、FET あたりのピーク時のエネルギー損失は 42W から 6.7W に低減するだけです (全体的な効率にプラスの影響を与えます)。