SLAAE74A December 2022 – March 2023 MSP430AFE221 , MSP430AFE222 , MSP430AFE223 , MSP430AFE231 , MSP430AFE232 , MSP430AFE233 , MSP430AFE251 , MSP430AFE252 , MSP430AFE253 , MSP430BT5190 , MSP430F1101 , MSP430F1101A , MSP430F1111A , MSP430F112 , MSP430F1121 , MSP430F1121A , MSP430F1122 , MSP430F1132 , MSP430F122 , MSP430F1222 , MSP430F123 , MSP430F1232 , MSP430F133 , MSP430F135 , MSP430F147 , MSP430F1471 , MSP430F148 , MSP430F1481 , MSP430F149 , MSP430F1491 , MSP430F155 , MSP430F156 , MSP430F157 , MSP430F1610 , MSP430F1611 , MSP430F1612 , MSP430F167 , MSP430F168 , MSP430F169 , MSP430F2001 , MSP430F2002 , MSP430F2003 , MSP430F2011 , MSP430F2012 , MSP430F2013 , MSP430F2013-EP , MSP430F2101 , MSP430F2111 , MSP430F2112 , MSP430F2121 , MSP430F2122 , MSP430F2131 , MSP430F2132 , MSP430F2132-EP , MSP430F2232 , MSP430F2234 , MSP430F2252 , MSP430F2254 , MSP430F2272 , MSP430F2274 , MSP430F2274-EP , MSP430F233 , MSP430F2330 , MSP430F235 , MSP430F2350 , MSP430F2370 , MSP430F2410 , MSP430F2416 , MSP430F2417 , MSP430F2418 , MSP430F2419 , MSP430F247 , MSP430F2471 , MSP430F248 , MSP430F2481 , MSP430F249 , MSP430F249-EP , MSP430F2491 , MSP430F2616 , MSP430F2617 , MSP430F2618 , MSP430F2619 , MSP430F2619S-HT , MSP430F412 , MSP430F413 , MSP430F4132 , MSP430F415 , MSP430F4152 , MSP430F417 , MSP430F423 , MSP430F423A , MSP430F425 , MSP430F4250 , MSP430F425A , MSP430F4260 , MSP430F427 , MSP430F4270 , MSP430F427A , MSP430F435 , MSP430F4351 , MSP430F436 , MSP430F4361 , MSP430F437 , MSP430F4371 , MSP430F438 , MSP430F439 , MSP430F447 , MSP430F448 , MSP430F4481 , MSP430F449 , MSP430F4491 , MSP430F4616 , MSP430F46161 , MSP430F4617 , MSP430F46171 , MSP430F4618 , MSP430F46181 , MSP430F4619 , MSP430F46191 , MSP430F47126 , MSP430F47127 , MSP430F47163 , MSP430F47166 , MSP430F47167 , MSP430F47173 , MSP430F47176 , MSP430F47177 , MSP430F47183 , MSP430F47186 , MSP430F47187 , MSP430F47193 , MSP430F47196 , MSP430F47197 , MSP430F477 , MSP430F478 , MSP430F4783 , MSP430F4784 , MSP430F479 , MSP430F4793 , MSP430F4794 , MSP430F5131 , MSP430F5132 , MSP430F5151 , MSP430F5152 , MSP430F5171 , MSP430F5172 , MSP430F5212 , MSP430F5214 , MSP430F5217 , MSP430F5219 , MSP430F5222 , MSP430F5224 , MSP430F5229 , MSP430F5232 , MSP430F5234 , MSP430F5237 , MSP430F5239 , MSP430F5242 , MSP430F5244 , MSP430F5247 , MSP430F5249 , MSP430F5252 , MSP430F5253 , MSP430F5254 , MSP430F5255 , MSP430F5256 , MSP430F5257 , MSP430F5258 , MSP430F5259 , MSP430F5304 , MSP430F5308 , MSP430F5309 , MSP430F5310 , MSP430F5324 , MSP430F5325 , MSP430F5326 , MSP430F5327 , MSP430F5328 , MSP430F5328-EP , MSP430F5329 , MSP430F5333 , MSP430F5335 , MSP430F5336 , MSP430F5338 , MSP430F5340 , MSP430F5341 , MSP430F5342 , MSP430F5358 , MSP430F5359 , MSP430F5418 , MSP430F5418A , MSP430F5419 , MSP430F5419A , MSP430F5435 , MSP430F5435A , MSP430F5436 , MSP430F5436A , MSP430F5437 , MSP430F5437A , MSP430F5438 , MSP430F5438A , MSP430F5438A-EP , MSP430F5438A-ET , MSP430F5500 , MSP430F5501 , MSP430F5502 , MSP430F5503 , MSP430F5504 , MSP430F5505 , MSP430F5506 , MSP430F5507 , MSP430F5508 , MSP430F5509 , MSP430F5510 , MSP430F5513 , MSP430F5514 , MSP430F5515 , MSP430F5517 , MSP430F5519 , MSP430F5521 , MSP430F5522 , MSP430F5524 , MSP430F5525 , MSP430F5526 , MSP430F5527 , MSP430F5528 , MSP430F5529 , MSP430F5630 , MSP430F5631 , MSP430F5632 , MSP430F5633 , MSP430F5634 , MSP430F5635 , MSP430F5636 , MSP430F5637 , MSP430F5638 , MSP430F5658 , MSP430F5659 , MSP430F6433 , MSP430F6435 , MSP430F6436 , MSP430F6438 , MSP430F6458 , MSP430F6459 , MSP430F6459-HIREL , MSP430F6630 , MSP430F6631 , MSP430F6632 , MSP430F6633 , MSP430F6634 , MSP430F6635 , MSP430F6636 , MSP430F6637 , MSP430F6638 , MSP430F6658 , MSP430F6659 , MSP430F6720 , MSP430F6720A , MSP430F6721 , MSP430F6721A , MSP430F6723 , MSP430F6723A , MSP430F6724 , MSP430F6724A , MSP430F6725 , MSP430F6725A , MSP430F6726 , MSP430F6726A , MSP430F6730 , MSP430F6730A , MSP430F6731 , MSP430F6731A , MSP430F6733 , MSP430F6733A , MSP430F6734 , MSP430F6734A , MSP430F6735 , MSP430F6735A , MSP430F6736 , MSP430F6736A , MSP430F6745 , MSP430F67451 , MSP430F67451A , MSP430F6745A , MSP430F6746 , MSP430F67461 , MSP430F67461A , MSP430F6746A , MSP430F6747 , MSP430F67471 , MSP430F67471A , MSP430F6747A , MSP430F6748 , MSP430F67481 , MSP430F67481A , MSP430F6748A , MSP430F6749 , MSP430F67491 , MSP430F67491A , MSP430F6749A , MSP430F67621 , MSP430F67621A , MSP430F67641 , MSP430F67641A , MSP430F6765 , MSP430F67651 , MSP430F67651A , MSP430F6765A , MSP430F6766 , MSP430F67661 , MSP430F67661A , MSP430F6766A , MSP430F6767 , MSP430F67671 , MSP430F67671A , MSP430F6767A , MSP430F6768 , MSP430F67681 , MSP430F67681A , MSP430F6768A , MSP430F6769 , MSP430F67691 , MSP430F67691A , MSP430F6769A , MSP430F6775 , MSP430F67751 , MSP430F67751A , MSP430F6775A , MSP430F6776 , MSP430F67761 , MSP430F67761A , MSP430F6776A , MSP430F6777 , MSP430F67771 , MSP430F67771A , MSP430F6777A , MSP430F6778 , MSP430F67781 , MSP430F67781A , MSP430F6778A , MSP430F6779 , MSP430F67791 , MSP430F67791A , MSP430F6779A , MSP430FE423 , MSP430FE4232 , MSP430FE423A , MSP430FE4242 , MSP430FE425 , MSP430FE4252 , MSP430FE425A , MSP430FE427 , MSP430FE4272 , MSP430FE427A , MSP430FG4250 , MSP430FG4260 , MSP430FG4270 , MSP430FG437 , MSP430FG438 , MSP430FG439 , MSP430FG4616 , MSP430FG4617 , MSP430FG4618 , MSP430FG4619 , MSP430FG477 , MSP430FG478 , MSP430FG479 , MSP430FG6425 , MSP430FG6426 , MSP430FG6625 , MSP430FG6626 , MSP430FR2000 , MSP430FR2032 , MSP430FR2033 , MSP430FR2100 , MSP430FR2110 , MSP430FR2111 , MSP430FR2153 , MSP430FR2155 , MSP430FR2310 , MSP430FR2311 , MSP430FR2353 , MSP430FR2355 , MSP430FR2422 , MSP430FR2433 , MSP430FR2475 , MSP430FR2476 , MSP430FR2512 , MSP430FR2522 , MSP430FR2532 , MSP430FR2533 , MSP430FR2632 , MSP430FR2633 , MSP430FR2672 , MSP430FR2673 , MSP430FR2675 , MSP430FR2676 , MSP430FR4131 , MSP430FR4132 , MSP430FR4133 , MSP430FR5041 , MSP430FR5043 , MSP430FR50431 , MSP430FR5720 , MSP430FR5721 , MSP430FR5722 , MSP430FR5723 , MSP430FR5724 , MSP430FR5725 , MSP430FR5726 , MSP430FR5727 , MSP430FR5728 , MSP430FR5729 , MSP430FR5730 , MSP430FR5731 , MSP430FR5732 , MSP430FR5733 , MSP430FR5734 , MSP430FR5735 , MSP430FR5736 , MSP430FR5737 , MSP430FR5738 , MSP430FR5739 , MSP430FR5739-EP , MSP430FR5847 , MSP430FR58471 , MSP430FR5848 , MSP430FR5849 , MSP430FR5857 , MSP430FR5858 , MSP430FR5859 , MSP430FR5867 , MSP430FR58671 , MSP430FR5868 , MSP430FR5869 , MSP430FR5870 , MSP430FR5872 , MSP430FR58721 , MSP430FR5887 , MSP430FR5888 , MSP430FR5889 , MSP430FR58891 , MSP430FR5922 , MSP430FR59221 , MSP430FR5947 , MSP430FR59471 , MSP430FR5948 , MSP430FR5949 , MSP430FR5957 , MSP430FR5958 , MSP430FR5959 , MSP430FR5962 , MSP430FR5964 , MSP430FR5967 , MSP430FR5968 , MSP430FR5969 , MSP430FR59691 , MSP430FR5970 , MSP430FR5972 , MSP430FR59721 , MSP430FR5986 , MSP430FR5987 , MSP430FR5988 , MSP430FR5989 , MSP430FR5989-EP , MSP430FR59891 , MSP430FR5992 , MSP430FR5994 , MSP430FR59941 , MSP430FR6005 , MSP430FR6007 , MSP430FR6035 , MSP430FR6037 , MSP430FR60371 , MSP430FR6041 , MSP430FR6043 , MSP430FR60431 , MSP430FR6045 , MSP430FR6047 , MSP430FR60471 , MSP430FR6820 , MSP430FR6822 , MSP430FR68221 , MSP430FR6870 , MSP430FR6872 , MSP430FR68721 , MSP430FR6877 , MSP430FR6879 , MSP430FR68791 , MSP430FR6887 , MSP430FR6888 , MSP430FR6889 , MSP430FR68891 , MSP430FR6920 , MSP430FR6922 , MSP430FR69221 , MSP430FR6927 , MSP430FR69271 , MSP430FR6928 , MSP430FR6970 , MSP430FR6972 , MSP430FR69721 , MSP430FR6977 , MSP430FR6979 , MSP430FR69791 , MSP430FR6987 , MSP430FR6988 , MSP430FR6989 , MSP430FR69891 , MSP430FW423 , MSP430FW425 , MSP430FW427 , MSP430FW428 , MSP430FW429 , MSP430G2001 , MSP430G2101 , MSP430G2102 , MSP430G2111 , MSP430G2112 , MSP430G2121 , MSP430G2131 , MSP430G2132 , MSP430G2152 , MSP430G2153 , MSP430G2201 , MSP430G2202 , MSP430G2203 , MSP430G2210 , MSP430G2211 , MSP430G2212 , MSP430G2213 , MSP430G2221 , MSP430G2230 , MSP430G2230-EP , MSP430G2231 , MSP430G2231-EP , MSP430G2232 , MSP430G2233 , MSP430G2252 , MSP430G2253 , MSP430G2302 , MSP430G2302-EP , MSP430G2303 , MSP430G2312 , MSP430G2313 , MSP430G2332 , MSP430G2332-EP , MSP430G2333 , MSP430G2352 , MSP430G2353 , MSP430G2402 , MSP430G2403 , MSP430G2412 , MSP430G2413 , MSP430G2432 , MSP430G2433 , MSP430G2444 , MSP430G2452 , MSP430G2453 , MSP430G2513 , MSP430G2533 , MSP430G2544 , MSP430G2553 , MSP430G2744 , MSP430G2755 , MSP430G2855 , MSP430G2955 , MSP430I2020 , MSP430I2021 , MSP430I2030 , MSP430I2031 , MSP430I2040 , MSP430I2041 , MSP430L092 , MSP430TCH5E , MSPM0C1103 , MSPM0C1104 , MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507 , MSPM0L1105 , MSPM0L1106 , MSPM0L1227 , MSPM0L1228 , MSPM0L1228-Q1 , MSPM0L1303 , MSPM0L1304 , MSPM0L1305 , MSPM0L1306 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346 , MSPM0L2227 , MSPM0L2228 , MSPM0L2228-Q1

- Abstract

- Trademarks

- 1Software Porting Flow

- 2Development Environments

- 3Migration Considerations

- 4Revision History

3.5 Event and Interrupt Handling

In MSP430 MCUs, the interrupt priorities are fixed and defined by the arrangement of the modules in the connection chain as shown in #GUID-B6FC135D-4C21-4BF7-8EBD-FE8C0C2A91C3. There are three types of interrupts: system reset, (non)maskable, and maskable.

Figure 3-1 MSP430 Event and Interrupt Handling

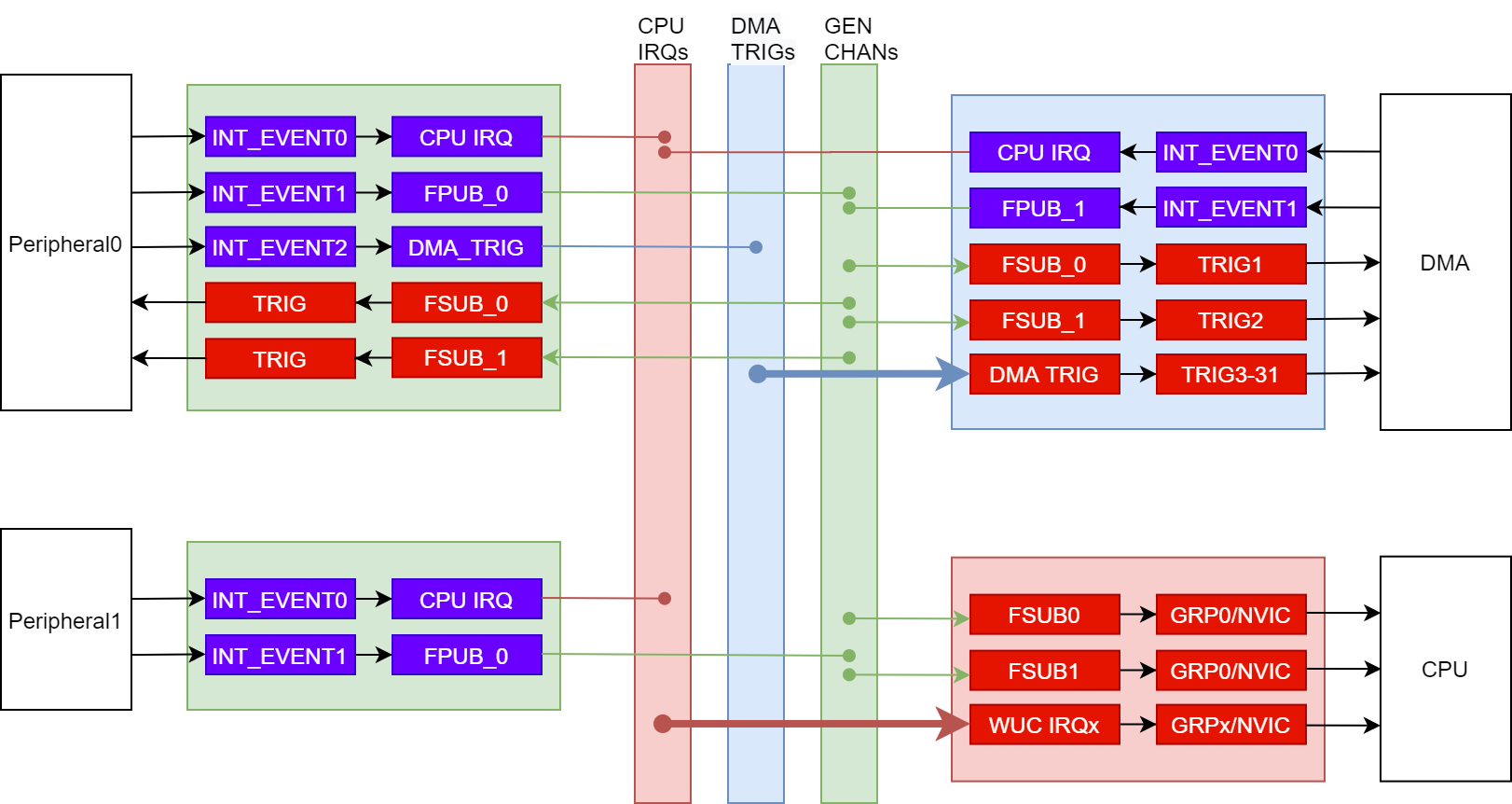

Figure 3-1 MSP430 Event and Interrupt HandlingMSPM0 MCUs have an event manager that transfers digital events from one entity to another. The event manager implements event transfer through a defined set of event publishers (generators) and subscribers (receivers) that are interconnected through an event fabric containing a combination of static and programmable routes.

Events that are transferred by the event manager include:

- Peripheral event transferred to the CPU as an interrupt request (IRQ)

- Peripheral event transferred to the DMA as a DMA trigger

- Peripheral event transferred to another peripheral to directly trigger an action in hardware

The event manager connects event publishers to event subscribers through an event fabric. There are three types of event fabric: static event routes, DMA event routes, and generic event routes.

#GUID-EB136935-E00C-4EB8-AE21-35BE4DB1F8E2 shows the event map. Different peripherals are routed through different event fabrics to achieve different event transitions. For more details, see the device technical reference manual.

Figure 3-2 MSPM0 Event and Interrupt Handling

Figure 3-2 MSPM0 Event and Interrupt Handling