SLUAAY2 December 2024 ISO5451 , ISO5451-Q1 , ISO5452 , ISO5452-Q1 , ISO5851 , ISO5851-Q1 , ISO5852S , ISO5852S-EP , ISO5852S-Q1 , UCC21710 , UCC21710-Q1 , UCC21717-Q1 , UCC21732 , UCC21732-Q1 , UCC21736-Q1 , UCC21737-Q1 , UCC21738-Q1 , UCC21739-Q1 , UCC21750 , UCC21750-Q1 , UCC21755-Q1 , UCC21756-Q1 , UCC21759-Q1

6.2 Safe Shutdown Considerations

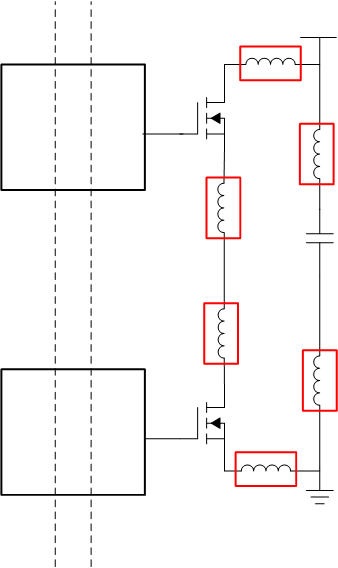

When safe shutdown is implemented, the power loop parasitic inductance plays a large role in the VCE/VDS overshoot profile and the shutdown time. Larger power loop parasitic inductance would increase the VCE/VDS overshoot with the same power switch di/dt, which is also why STO/2LTO are more desirable under this condition. Also, shutdown time can be reduced if parasitic inductance in the power loop is reduced. This includes power module stray inductance.

Figure 6-3 Power Loop Inductance

Figure 6-3 Power Loop Inductance