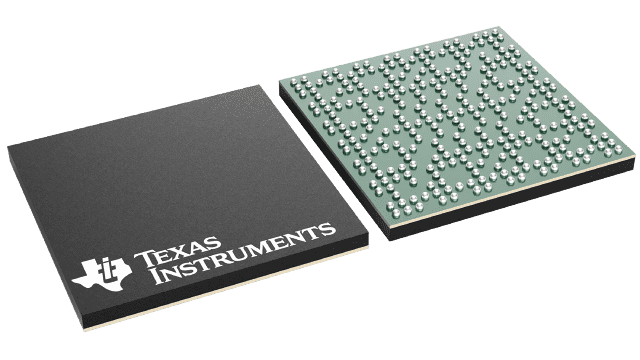

패키징 정보

| 패키지 | 핀 FCCSP (ALX) | 293 |

| 작동 온도 범위(°C) -40 to 125 |

| 패키지 수량 | 캐리어 1,000 | LARGE T&R |

AM2432의 주요 특징

- Up to 2× Dual-core Arm Cortex-R5F MCU subsystems operating at up to 800MHz, highly-integrated for

real-time processing

- Dual-core Arm Cortex-R5F clusters support dual-core and single-core operation

- 32KB I-cache and 32KB D-cache per R5F core with SECDED ECC on all memories

- Single-core: 128KB TCM per cluster (128KB TCM per R5F core)

- Dual-core: 128KB TCM per cluster (64KB TCM per R5F core)

- 1× Single-core Arm Cortex-M4F MCU at up to 400MHz

- 256KB SRAM with SECDED ECC

- Up to 2MB of On-chip RAM (OCSRAM) with

SECDED ECC:

- Can be divided into smaller banks in increments of 256KB for as many as 8 separate memory banks

- Each memory bank can be allocated to a single core to facilitate software task partitioning

- DDR Subsystem (DDRSS)

- Supports LPDDR4, DDR4 memory types

- 16-bit data bus with inline ECC

- Supports speeds up to 1600 MT/s

- Device Management Security Controller

(DMSC-L)

- Centralized SoC system controller

- Manages system services including initial boot, security, and clock/reset/power management

- Communication with various processing units over message manager

- Simplified interface for optimizing unused peripherals

- On-Chip Debug functionality through JTAG and Trace interfaces)

- Data Movement Subsystem (DMSS)

- Block Copy DMA (BCDMA)

- Packet DMA (PKTDMA)

- Secure Proxy (SEC_PROXY)

- Ring Accelerator (RINGACC)

- Time Sync Subsystem

- Central Platform Time Sync (CPTS) module

- Timer Manager (TIMERMANAGER) with 1024 timers

- Time Sync and Compare event interrupt routers

- 2× Gigabit Industrial Communication

Subsystems (PRU_ICSSG)

- Optional support for Profinet IRT, Profinet RT, EtherNet/IP, EtherCAT, Time-Sensitive Networking (TSN), and other Networking Protocols

- Backwards compatibility with 10/100Mb PRU-ICSS

- Each PRU_ICSSG contains:

- 3× PRU RISC Cores per Slice (2×

Slice per PRU_ICSSG)

- PRU General Use core (PRU)

- PRU Real-Time Unit core (PRU-RTU)

- PRU Transmit core (PRU-TX)

- Each PRU core supports the

following features:

- Instruction RAM with ECC

- Broadside RAM

- Multiplier with optional accumulator (MAC)

- CRC16/32 hardware accelerator

- Byte swap for Big/Little Endian conversion

- SUM32 hardware accelerator for UDP checksum

- Task Manager for preemption support

- Up to 2× Ethernet ports

- RGMII (10/100/1000)

- MII (10/100)

- Three Data RAMs with ECC

- 8 banks of 30 × 32-bit register scratchpad memory

- Interrupt controller and task manager

- 2× 64-bit Industrial Ethernet Peripherals (IEPs) for time stamping and other time synchronization functions

- 18× Sigma-Delta Filter Module

(SDFM) interfaces

- Short circuit logic

- Over-current logic

- 6× Multi-protocol position encoder interfaces

- 1× Enhanced Capture Module (ECAP)

- 16550-compatible UART

- Dedicated 192MHz clock to support 12Mbps PROFIBUS

- 3× PRU RISC Cores per Slice (2×

Slice per PRU_ICSSG)

- Secure boot supported

- Hardware-enforced Root-of-Trust (RoT)

- Support to switch RoT via backup key

- Support for takeover protection, IP

protection, and anti-roll back protection

- Cryptographic acceleration supported

- Session-aware cryptographic engine with ability to auto-switch key-material based on incoming data stream

- Supports cryptographic cores

- AES – 128-/192-/256-Bit key sizes

- 3DES – 56-/112-/168-Bit key sizes

- MD5, SHA1

- SHA2 – 224-/256-/384-/512-Bit key sizes

- DRBG with true random number generator

- PKA (Public Key Accelerator) to Assist in RSA/ECC processing for secure boot

- DMA support

- Debugging security

- Extensive firewall support for isolation

- Secure watchdog/timer/IPC

- Secure storage support

- On-the-Fly encryption support for OSPI interface in XIP mode

- Networking security support for data (Payload) encryption/authentication via packet based hardware cryptographic engine

- Security co-processor (DMSC-L) for key and security management, with dedicated device level interconnect for security

- 6× Inter-Integrated Circuit (I2C) ports

- 9× Universal Asynchronous Receive/Transmit (UART) modules

- 1× 12-bit Analog-to-Digital Converters

(ADC)

- Configurable sample rate up to 4MSPS

- 8× multiplexed analog inputs

- 7× Multichannel Serial Peripheral Interfaces (SPI) controllers

- 3× General-Purpose I/O (GPIO) modules

- 9× Enhanced Pulse-Width Modulator (EPWM) modules

- 3× Enhanced Capture (ECAP) modules

- 3× Enhanced Quadrature Encoder Pulse (EQEP) modules

- 2× Modular Controller Area Network (MCAN) modules with full CAN-FD support

- 2× Fast Serial Interface Transmitter (FSITX) cores

- 6× Fast Serial Interface Receiver (FSIRX) cores

High-speed interfaces:

- 1× Integrated Ethernet switch supporting:

(CPSW)

- Up to 2 external Ethernet ports

- RGMII (10/100/1000)

- RMII (10/100)

- IEEE 1588 (2008 Annex D, Annex E, Annex F) with 802.1AS PTP

- Clause 45 MDIO PHY management

- Energy efficient Ethernet (802.3az)

- Up to 2 external Ethernet ports

- 1× PCI-Express Gen2 controller (PCIE)

- Supports Gen2 Single Lane operation

- 1× USB 3.1 Dual-Role Device (DRD)

Subsystem (USBSS)

- Port configurable as USB Host, USB Device, or USB Dual-Role device

- USB Device: High-speed (480Mbps) and Full-speed (12Mbps)

- USB Host: SuperSpeed Gen1 (5Gbps), High-speed (480Mbps), Full-speed (12Mbps), and Low-speed (1.5Mbps)

- Integrated USB VBUS detection

- 1× Serializer/Deserializer (SERDES)

- One SERDES PHY lane to support eitherPCI-Express Gen2 or USB SuperSpeed Gen1

- 2× Multimedia Card/Secure Digital (MMCSD)

interfaces

- One 8-bit for eMMC (MMCSD0)

- One 4-bit for MMCSD/SDIO (MMCSD1)

- Integrated analog switch for voltage switching from 3.3V to 1.8V for high-speed cards

- 1× General-Purpose Memory Controller

(GPMC)

- 16-bit parallel bus with 133MHz clock or

- 32-bit parallel bus with 100MHz clock

- Error Location Module (ELM) support

- 1× Flash Subsystem (FSS) for external

memory configurable as either:

- 1× Octal SPI (OSPI) flash interface

- or 1× Quad SPI (QSPI) flash interface

- Simplified power sequencing requirements

- Dual-voltage I/O Support (3.3V / 1.8V)

- Integrated SDIO LDO for handling automatic voltage transition for SD interface

- Integrated voltage supervisor for monitoring over-voltage and under-voltage conditions

- Integrated power supply glitch detector for detecting fast supply transients

Functional safety:

-

Functional Safety-Compliant

- Developed for functional safety applications

- Documentation available to aid IEC 61508 functional safety system design

- Systematic capability up to SIL 3

- Hardware integrity up to SIL 2

- Safety-related certification

- ECC or parity on calculation-critical memories

- Built-In Self-Test (BIST) for CPU and on-chip RAM

- Error Signaling Module (ESM) with dedicated error pin

- ECC and parity on select internal bus interconnects

- Run-time safety diagnostics,

including:

- Voltage, Temperature, and Clock Monitoring

- Windowed Watchdog Timers

- CRC Engine for memory integrity checks

- MCU domain with dedicated memory,

interfaces, and M4FSS capable of isolation from the larger SoC with Freedom From

Interference (FFI) features:

- Separate interconnect

- Firewalls and timeout gaskets

- Controlled reset isolation

- Dedicated MCU PLL and MMR control

- Separate I/O voltage supply rail

- Supports boot from OSPI/QSPI Flash, SPI Flash, parallel NOR Flash, parallel NAND Flash, UART, I2C, MMCSD, eMMC, USB, PCIe, and Ethernet interfaces.

- 16-nm FinFET technology

- ALV: 17.2mm × 17.2mm, 0.8mm pitch(441-pin) [Lidded] Flip-Chip Ball Grid Array(FCBGA)

- ALX: 11.0mm × 11.0mm, 0.5mm pitch(293-pin) [Overmolded] Flip-Chip Chip Scale Package(FCCSP)

AM2432에 대한 설명

AM243x is an extension of Sitara’s industrial-grade portfolio into high-performance microcontrollers. The AM243x device is built for industrial applications, such as motor drives and remote I/O modules, which require a combination of real-time communications and processing. The AM243x family provides scalable performance with up to four Cortex-R5F MCUs, one Cortex-M4F, and two instances of Sitara’s gigabit TSN-enabled PRU_ICSSG.

The AM243x SoC architecture was designed to provide best-in-class real-time performance through the high-performance Arm Cortex-R5F cores, Tightly-Coupled Memory (TCM) banks, configurable SRAM partitioning, and dedicated low-latency paths to and from peripherals for rapid data movement in and out of the SoC. This deterministic architecture allows for AM243x to handle the tight control loops found in servo drives while the peripherals like FSI, GPMC, ECAPs, PWMs, and encoder interfaces help enable a number of different architectures found in these systems.

The SoC provides flexible industrial communications capability including full protocol stacks for EtherCAT target, PROFINET device, EtherNet/IP adapter, and IO-Link Controller. The PRU_ICSSG further provides capability for gigabit and TSN based protocols. In addition, the PRU_ICSSG enables additional interfaces including a UART interface, sigma delta decimation filters, and absolute encoder interfaces.

Functional safety features can be enabled through the integrated Cortex-M4F along with dedicated peripherals which can all be isolated from the rest of the SoC. AM243x also supports secure boot.