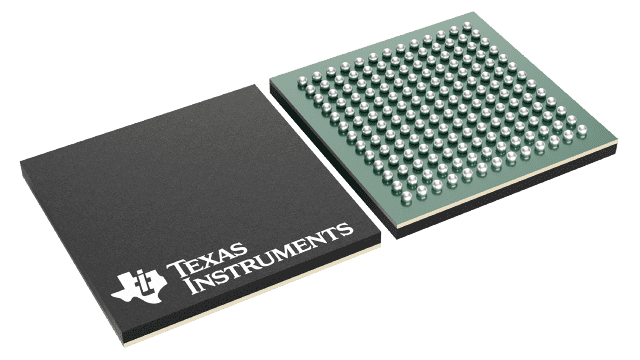

パッケージ情報

| パッケージ | ピン数 NFBGA (ZWS) | 169 |

| 動作温度範囲 (℃) -40 to 85 |

| パッケージ数量 | キャリア 1,000 | LARGE T&R |

XIO2001 の特徴

- フル ×1 PCI Express™ スループット

- 「PCI Express to PCI/PCI-X Bridge Specification」リビジョン 1.0 に完全準拠

- 「PCI Express Base Specification」リビジョン 2.0 に完全準拠

- 「PCI Local Bus Specification」リビジョン 2.3 に完全準拠

- ECRC サポートなど、PCI Express の高度なエラー報告機能

- D1、D2、D3 hot、D3 cold をサポート

- アクティブ状態リンクのパワー・マネージメントにより、L0 と L1 の両方の状態を使用して PCI Express リンクのパケット・アクティビティがアイドルのときに電力を節約できます

- ウェイク・イベントとビーコンのサポート

- PCI Express データ・ポイズニングおよび PCI バス・パリティ・エラーなどのエラー転送

- 100MHz の差動 PCI Express 共通リファレンス・クロックまたは 125MHz のシングルエンド・リファレンス・クロックを使用

- オプションのスペクトラム拡散リファレンス・クロックがサポートされています

- トランザクション・レイテンシを最小限に抑える堅牢なパイプライン・アーキテクチャ

- フル PCI ローカル・バス 66MHz/32 ビットのスループット

- 内部構成可能な 2 レベル優先順位設定方式により、6 つの下位 PCI バス・マスタをサポート

- 最大 6 つの外部 PCI マスタをサポートする内部 PCI アービタ

- シリアル IRQ 割り込み用の高度な PCI Express メッセージ信号割り込み生成

- 外部 PCI バス・アービタ・オプション

- PCI Bus LOCK サポート

- 製造試験の JTAG/BS

- PCI-Express CLKREQ サポート

- クロック実行および電源オーバーライドのサポート

- 6 つのバッファ付き PCI クロック出力 (25MHz、33MHz、50MHz、66MHz)

- PCI バス・インターフェイスの 3.3V および 5.0V (5.0V で 25MHz または 33MHz のみ) 許容誤差オプション

- 主電源がオフのときは V AUX のみの消費電力となる AUX パワー・スイッチを内蔵

- 5 つの 3.3V、マルチファンクション、汎用 I/O 端子

- アドイン・カードの PCI Express のパワー・バジェット / 制限拡張をサポートしているメモリマップ EEPROM シリアル・バス・コントローラ

- コンパクトなフットプリント、鉛フリー 144 ボール、ZAJ nFBGA、鉛フリー 169 ボール ZWS nFBGA、PowerPAD™ HTQFP 128 ピン PNP パッケージ

XIO2001 に関する概要

XIO2001 は、「PCI Express to PCI/PCI-X Bridge Specification」リビジョン 1.0 に完全準拠した、単一機能 PCI Express から PCI への変換ブリッジです。 ダウンストリーム・トラフィックの場合、ブリッジは同時に最大 8 つの投稿トランザクションと 4 つの非投稿トランザクションをサポートします。アップストリーム・トラフィックの場合、最大 6 つの投稿トランザクションと 4 つの非投稿トランザクションが同時にサポートされます。

PCI Expressインターフェイスは、「PCI Express Base Specification」リビジョン 2.0 に完全準拠しています。

PCI Express インターフェイスは、各方向で同時に 250MB/秒のフル・パケット・スループットで動作する ×1 リンクをサポートしています。また、このブリッジは、「PCI Express Base Specification」で定義されている拡張 CRC (ECRC) などの高度なエラー報告機能もサポートしています。 これらの機能を最大限に活用するには、補助的なファームウェアまたはソフトウェアが必要です。